瑞士洛桑联邦理工学院团队近期 Nature 发表其在存内计算芯片研究上的新成果,他们通过单一体系结构将逻辑运算和数据存储两种功能模块有效整合到了一起,可提高计算系统中的信息传输效率,降低能源消耗,这为更高能效的超级计算机的开发提供了新的助力。

研究背景

集成电路产业一路走来,已经沿着摩尔定律发展超过40年,在降低芯片的尺寸、成本和功耗方面取得了巨大的进步。从1956年Univac I(第一台商用电子计算机,采用真空管,每秒1900次浮点操作消耗125千瓦)到今天的超级计算机(最新超算榜单第一的日本“富岳”测试结果达到每瓦16.9GFlops),浮点操作的功耗成本降低超过1万亿倍。

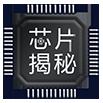

关于计算和存储,有许多巧妙的方法可以提高冯•诺伊曼架构的功耗效率,它们都指向了“更靠近内存”这一思路,即:使内存更接近逻辑单元——将不同的芯片紧密地封装在一起,亦或是在将存储单元和逻辑单元集成在同一片晶圆上。以目前排名第一的日本超算 “富岳” 所搭载的 A64FX 为例,其芯片就采用了融合 CPU+GPU 的异构计算架构*,使用7nm工艺制造并且内置了 7nm 的 HBM2 存储器,浮点性能2.7TFLOPS,配备32GB规格的HBM2内存,带宽达到了1TB/s。该处理器的计算单元与存储单元,尽管高度集成(采用了台积电CoWos封装工艺*),但二者仍然是分离的。

富士通所展示的A64FX晶圆照片

业界通过前述这种“缩短路径”的方法在提高计算的功耗效率方面取得了很大的进步的同时,生物学已经设计了一种更节能的策略,即把数据存放在大脑中,也就是把数据存储在计算的地方。通过检查一个典型突触/神经元的权重或调整它的值来驱动生物信号。这比通过两个不同的单元之间的电路——无论是在电路板上或是芯片内的电路——来回传输数据要省电得多。

在这样的设计思路,洛桑联邦理工学院团队通过类人脑的结构研究开发能将存储单元和计算单元合二为一的存内计算芯片。相关成果以“Logic-in-memory based on an atomically thin semiconductor”为题发表在期刊《Nature》。论文第一作者为博士研究生Guilherme Migliato Marega,通讯作者为Andras Kis教授,由洛桑联邦理工学院电气工程学院、生物工程学院和材料科学院研究人员共同完成。

*异构计算:异构计算主要是指使用不同类型指令集和体系架构的计算单元组成系统的计算方式,通俗来说即“CPU+X”的结构,例如与前述“富岳”同为超算领域的天河2号和神威太湖之光的处理器、AMD的APU都可算作异构计算的范围内。

*CoWoS,全称Chip On Wafer On Substrate,先将多颗裸芯片通过名为CoW(Chip on Wafer)的封装工艺连接至硅晶圆,再把CoW与基板(Substrate)连接,整合成CoWos模块。

制备方法

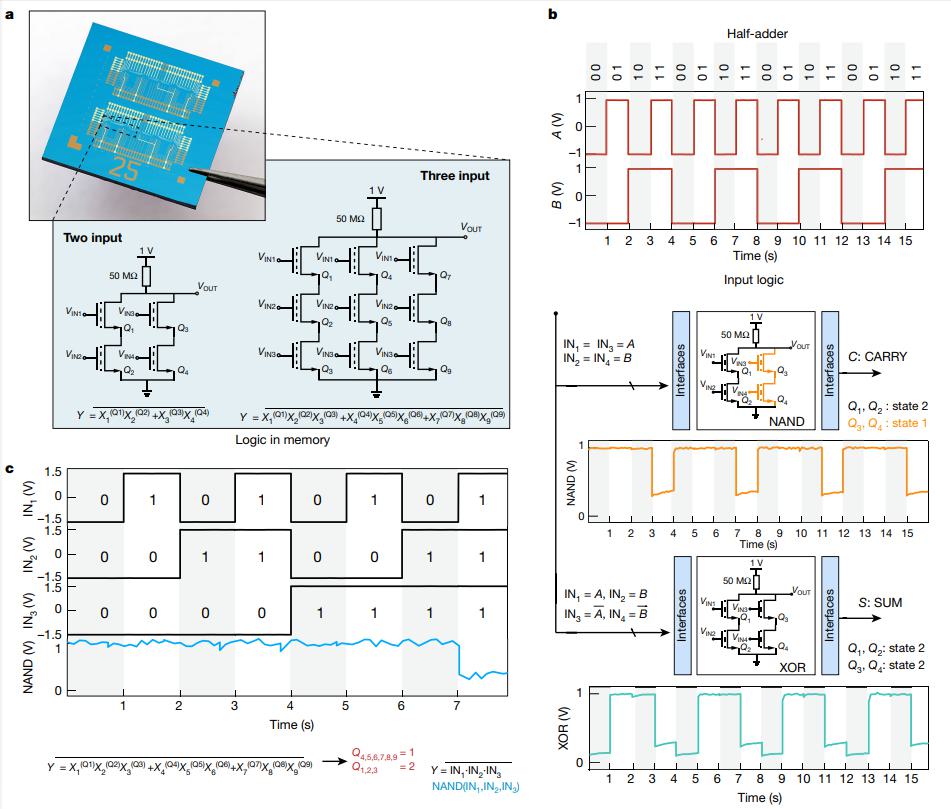

该团队采用二硫化钼(MoS2)作为通道材料,并将其用于开发基于浮栅场效应晶体管*(FGFETs)的存内计算芯片。在演示可编程或非门之后,浮栅晶体管作为适用于可重构逻辑回路的构建模块,可应用在更复杂的可编程逻辑上。

滑动查看完整结构图

图为芯片结构示意图,最下(由下至上)分别为硅衬底、氧化硅绝缘层、金属底栅、金属浮栅,两栅之间由30nm的HfO2阻挡层隔开。沟道与浮动栅由HfO2隧穿氧化物隔开。

*浮栅场效应晶体管,浮栅场效应管是闪存的单元位,是一种特殊的MOS管。这种MOS晶体管有两个多晶硅形成的栅极, 其中一个有电气连接, 叫控制栅;另外一个栅无外引, 是浮空的, 所以称之为浮栅。

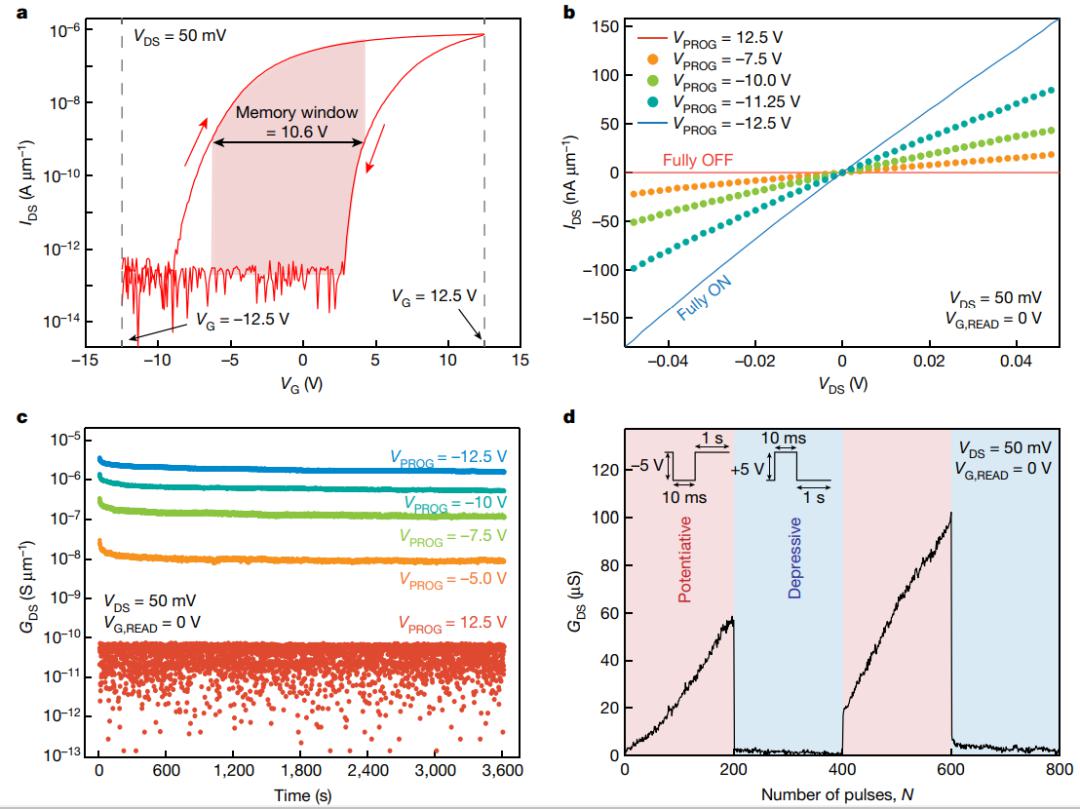

部分测试图

图为存储单元特性测试图

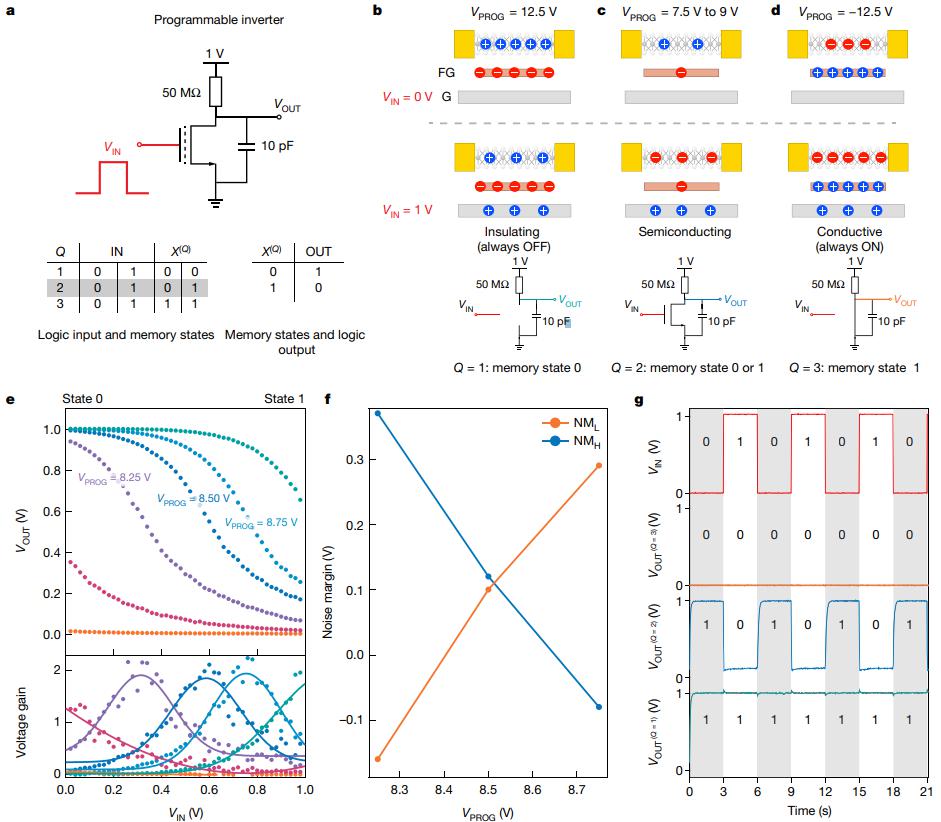

可编程逻辑门示意图

存内计算芯片的门电路结构和特性

前景展望

随着大数据时代对计算速度和性能要求的不断提高,数据在存储单元和计算单元之间的功耗会不断增大。据英特尔估计,超算应用中超过60%的能源都被消耗数据通信上,各国科学家都在致力于降低超算功率,而本项研究成果以不同于冯·诺依曼架构(计算与存储的分离)的设计思路实现存储计算二合一,大大减少了在存储器单元和处理器之间传输数据相关的能量损失,降低了计算所需的能源和时间。

当然这类探索目前还都处于实验阶段,尚未踏上商用道路,在国内,2019年清华大学类脑计算团队发表的“天机芯”类脑芯片、美国DARPA的IPU芯片,都是这一研究方向上的重要成果,他们为体积更小、性能更强、更节能的高性能计算提供了更多的可能。

论文全文链接:

https://www.nature.com/articles/s41586-020-2861-0

往期链接

| |||

| |||

| |||

|

关注更多栏目

●

●

●

●

●

●