иҝ‘ж—ҘпјҢеә”з”Ёжқҗж–ҷе…¬еҸёеңЁIEEE SISPADпјҲеӣҪйҷ…еҚҠеҜјдҪ“е·ҘиүәдёҺеҷЁд»¶д»ҝзңҹдјҡи®®пјүдёҠеҸ‘иЎЁдәҶе…¬еҸёз ”еҸ‘еӣўйҳҹеңЁ3nmе…ҲиҝӣиҠӮзӮ№дёӢй’ҲеҜ№TSVзЎ…йҖҡеӯ”зҡ„зү№еҫҒе°әеҜёдёҺз”өзү№жҖ§дёҺд№Ӣй—ҙе…ізі»з ”з©¶пјҢ并жүҫеҲ°дәҶдҪҝйҖҡеӯ”е…·жңүжңҖдҪіз”өжҖ§иғҪзҡ„зү№еҫҒе°әеҜёпјҢиҜҰжғ…иҜ·и§ҒжӯЈж–ҮгҖӮ

з ”з©¶иғҢжҷҜ

еңЁйӣҶжҲҗз”өи·ҜеҸ‘еұ•еҺҶзЁӢдёӯпјҢж‘©е°”е®ҡеҫӢиө·еҲ°дәҶйқһеёёйҮҚиҰҒзҡ„жҢҮеј•дҪңз”ЁпјҢиҖҢеңЁжҠҖжңҜиҠӮзӮ№дёҚж–ӯиҝӣжӯҘзҡ„иҝҮзЁӢдёӯпјҢжј”еҢ–еҮәдәҶдёҚеҗҢзҡ„жҠҖжңҜйҒ“и·ҜгҖӮе…¶дёӯд№ӢдёҖзҡ„вҖңMore Moore вҖқпјҢжҳҜжғіеҠһжі•жІҝзқҖж‘©е°”е®ҡеҫӢзҡ„йҒ“и·Ҝ继з»ӯеҫҖеүҚжҺЁиҝӣпјҢдёҚж–ӯзј©е°Ҹжҷ¶дҪ“з®Ўзҡ„зү№еҫҒе°әеҜёпјӣиҖҢеҸҰдёҖдёӘж–№еҗ‘зҡ„вҖңMore than Moore вҖқпјҲи¶…и¶Ҡж‘©е°”пјүеҒҡзҡ„жҳҜеҸ‘еұ•еңЁд№ӢеүҚж‘©е°”е®ҡеҫӢжј”иҝӣиҝҮзЁӢдёӯжүҖжңӘејҖеҸ‘зҡ„йғЁеҲҶпјҢе…Ҳиҝӣе°ҒиЈ…дҫҝжҳҜвҖңMore than Moore вҖқзҡ„дёҖз§ҚйҮҚиҰҒзҡ„е®һзҺ°и·Ҝеҫ„гҖӮ

TSVпјҲThrough Silicon ViaпјҢ зЎ…йҖҡеӯ”жҠҖжңҜпјүжҠҖжңҜжҳҜе…Ҳиҝӣе°ҒиЈ…дёӯжһҒе…·д»ЈиЎЁжҖ§зҡ„дёҖз§Қй«ҳеҜҶеәҰе°ҒиЈ…жҠҖжңҜпјҢиҝҷйЎ№жҠҖжңҜдҪҝеҫ—дёҚеҗҢиҠҜзүҮзҡ„жҷ¶еңҶиЈёзүҮеҸҜд»ҘеңЁжҷ¶еңҶиҖҢдёҚжҳҜPCBжқҝдёҠзӣҙжҺҘе®һзҺ°й«ҳеҜҶеәҰзҡ„дә’иҝһпјҢд№ҹиў«и®ӨдёәжҳҜ第еӣӣд»Је°ҒиЈ…жҠҖжңҜгҖӮеңЁTSVжҠҖжңҜдёӯпјҢдҪңдёәеұӮй—ҙз”өи·ҜиҝһжҺҘйҖҡйҒ“зҡ„йҖҡеӯ”еӨ§е°Ҹе’ҢдҪҚзҪ®зҡ„и®ҫи®ЎйңҖиҰҒиҖғиҷ‘иҜёеӨҡеӣ зҙ пјҡе°Ҹзҡ„еӯ”еҫ„еҸҜд»ҘиҺ·еҫ—жӣҙзҙ§еҮ‘зҡ„з©әй—ҙпјҢжӣҙеӨ§е°әеҜёзҡ„йҖҡеӯ”еҲҷиғҪеҮҸе°‘з”өйҳ»д»ҘжҸҗдҫӣжӣҙеҠ зҡ„з”өжҖ§иғҪгҖӮ

иҝ‘ж—ҘпјҢеә”з”Ёжқҗж–ҷе…¬еҸёзҡ„з ”з©¶еӣўйҳҹеұ•зӨәдәҶ他们еңЁйҖҡеӯ”еӯ”еҫ„дёҠзҡ„з ”з©¶жҲҗжһңпјҢеңЁ3nmжҠҖжңҜиҠӮзӮ№дёӢпјҢ他们еңЁеӯ”еҫ„еўһеӨ§зҡ„еёҰжқҘзҡ„дёҖжӯЈдёҖиҙҹзҡ„зӣёеҸҚжҖ§иғҪеўһзӣҠд№Ӣй—ҙжүҫеҲ°иҺ·еҫ—жңҖдҪіжҖ§иғҪзҡ„е№іиЎЎзӮ№гҖӮ

иҜҘз ”з©¶жҲҗжһңиҝ‘жңҹвҖңVia Size Optimization for Optimum Circuit Performance at 3 nm nodeвҖқдёәйўҳдәҺжөӢиҜ•йўҶеҹҹйЎ¶зә§дјҡи®®гҖҠIEEE SISPADгҖӢпјҲIEEEеӣҪйҷ…еҚҠеҜјдҪ“е·ҘиүәдёҺеҷЁд»¶д»ҝзңҹдјҡи®®пјүзҡ„2020е№ҙеәҰдјҡи®®дёҠйҰ–ж¬ЎеҸ‘иЎЁпјҢеә”з”Ёжқҗж–ҷе…¬еҸёзҡ„Sushant MittalгҖҒAshish Palзӯү6дәәдёәжң¬ж–Үе…ұеҗҢдҪңиҖ…гҖӮ

е®һйӘҢз»“и®ә

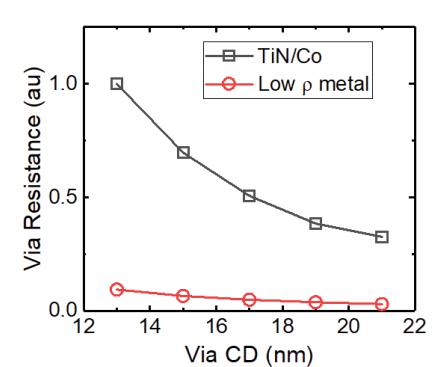

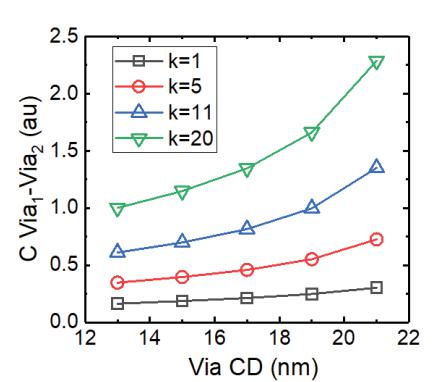

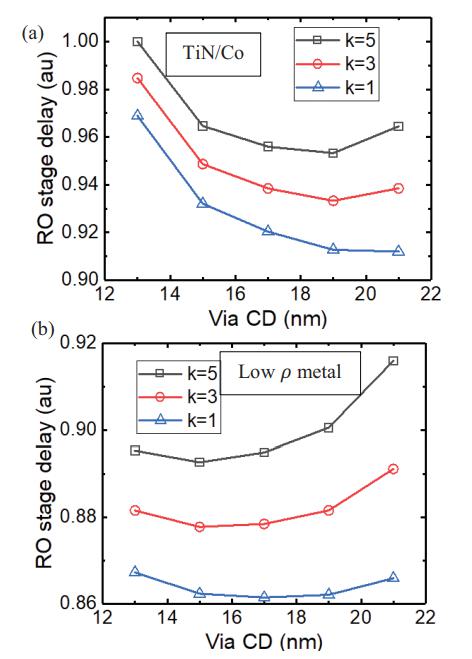

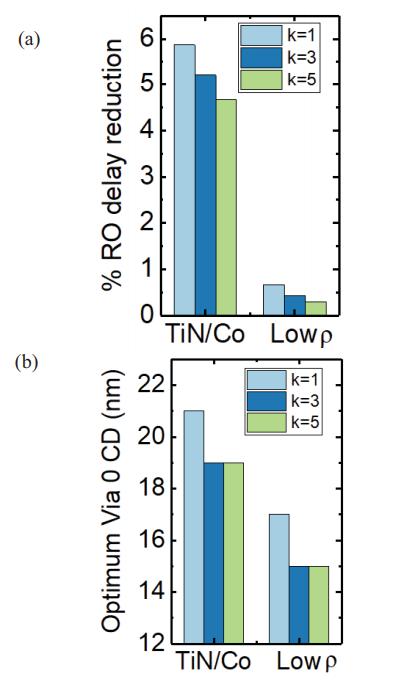

йҖҡеӯ”еӨ§е°Ҹзҡ„и®ҫи®ЎйҖҡеёёиҰҒиҖғиҷ‘дёӨеӨ§зӮ№пјҡдёҖжҳҜеҰӮдҪ•еңЁе…ҲиҝӣжҠҖжңҜиҠӮзӮ№дёӯжҸҗеҚҮе°ҒиЈ…еҜҶеәҰд»ҘиҺ·еҫ—жӣҙе°Ҹзҡ„дҪ“з§ҜпјҢдәҢжҳҜеңЁжӣҙе°Ҹзҡ„з”өеҺӢдёӢиҺ·еҫ—жӣҙй«ҳзҡ„з”өжөҒеҜҶеәҰпјҢдҪҶиҝҷдјҡдҪҝдҪ“з§ҜеҸҳеӨ§гҖӮйҖҡеёёеңЁз”өи·ҜеёғеұҖпјҲlayoutпјүйҳ¶ж®өдёҚдјҡиҖғиҷ‘йҖҡеӯ”жқҗж–ҷе’ҢйҖҡеӯ”д»ӢиҙЁеұӮжқҗж–ҷзҡ„йҖүжӢ©пјҢиҖҢйҖҡеӯ”еӨ§е°Ҹзҡ„еўһйҮҸдјҡдҪҝйҖҡеӯ”з”өйҳ»зҡ„еҮҸе°Ҹд»ҘжҸҗеҚҮжҖ§иғҪгҖӮжң¬йЎ№жҲҗжһңзҡ„з ”з©¶еӣўйҳҹз ”з©¶дәҶеҰӮдҪ•йҖҡиҝҮеўһеҠ йҖҡеӯ”зү№еҫҒе°әеҜёд»ҘеёҰжқҘжңҖдҪізҡ„жҖ§иғҪеўһзӣҠпјҢ并жүҫеҲ°дәҶйҖҡеӯ”еўһеҠ иҝҮзЁӢдёӯз”өйҳ»еҮҸе°Ҹvsз”өе®№еўһеҠ иҝҷдёҖжӯЈдёҖеҸҚдёӨз§Қж•Ҳеә”зҡ„е№іиЎЎзӮ№пјҢе…¶дё»иҰҒзҡ„еҪұе“Қеӣ зҙ жҳҜйҖҡеӯ”жқҗж–ҷзҡ„з”өйҳ»зҺҮе’ҢеұӮй—ҙд»ӢиҙЁзҡ„д»Ӣз”өеёёж•°гҖӮйҖҡеӯ”и®ҫи®Ўжқҗж–ҷдҪҝз”ЁдәҶTiN/Coжқҗж–ҷдҪ“зі»е’ҢдёҖз§Қз”өйҳ»зҺҮдёәй’ҙжқҗж–ҷ1/10зҡ„йҮ‘еұһжқҗж–ҷгҖӮ

зӣёе…іжөӢиҜ•

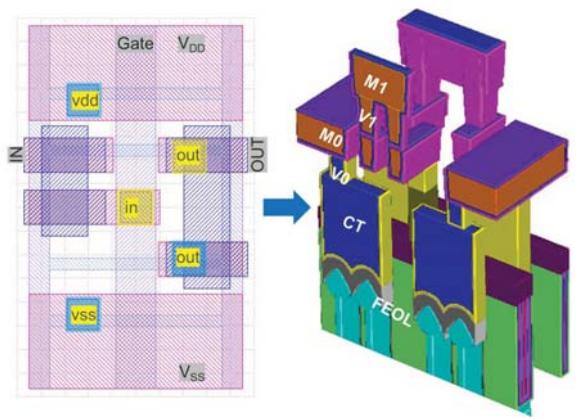

еӣҫпјҲ1пјүпјҡ3nmжҠҖжңҜиҠӮзӮ№зҡ„еҸҚзӣёеҷЁпјҲinverterпјүеҚ•е…ғи®ҫи®ЎеӣҫдёҺеҗҺз«Ҝе·ҘиүәдёӢзҡ„еҺҹзҗҶжЁЎеһӢ

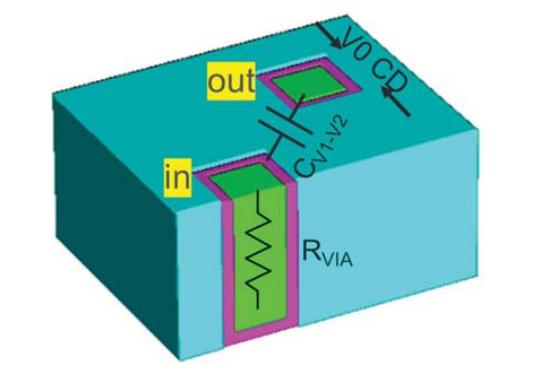

еӣҫпјҲ2пјүпјҡжң¬з ”究дёӯеүҚз«ҜдёҺеҗҺз«Ҝе·Ҙиүәзҡ„дё»иҰҒеҸӮж•°

еӣҫпјҲ3пјүпјҡйҖҡеӯ”0иҫ“е…Ҙиҫ“еҮәз«Ҝзҡ„з”өйҳ»дёҺз”өе®№зӨәж„ҸеӣҫпјҢ

йҖҡеӯ”0еңЁеӣҫпјҲ1пјүдёӯе·Іж ҮеҮә

ж»‘еҠЁжҹҘзңӢжүҖжңүеӣҫзүҮ

еӣҫ(4)пјҡдёӨз§ҚдёҚеҗҢжқҗж–ҷдҪ“зі»дёӯйҖҡеӯ”0зҡ„з”өйҳ»еҸҳеҢ–еҜ№жҜ”пјӣ

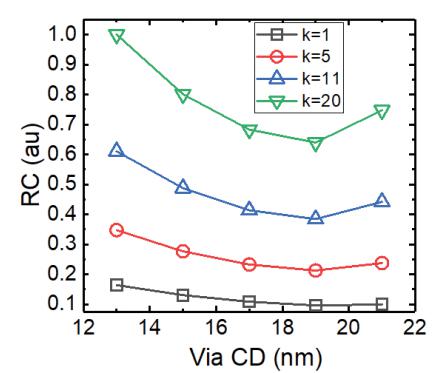

еӣҫ(5)пјҡдёҚеҗҢз”өд»Ӣеёёж•°дёӢзҡ„йҖҡеӯ”й—ҙз”өе®№еҜ№жҜ”пјӣ

еӣҫ(6)пјҡRCж—¶й—ҙдёҺTiN/CoдҪ“зі»зҡ„йҖҡеӯ”зү№еҫҒе°әеҜёй—ҙзҡ„е…ізі»

еӣҫпјҲ7пјүпјҡдёӨз§Қжқҗж–ҷдҪ“зі»дёӢзҡ„ROпјҲзҺҜеҪўйңҮиҚЎпјү延иҝҹеҜ№жҜ”

еӣҫпјҲ8пјүпјҡRO延иҝҹеҮҸе°‘йҮҸеҸҠзү№еҫҒе°әеҜёеҜ№жҜ”

еүҚжҷҜеұ•жңӣ

зӣ®еүҚпјҢиҠҜзүҮеҲ¶зЁӢе·Із»Ҹиө°еҲ°5nmиҠӮзӮ№пјҢеңЁдёҚиҝңзҡ„жңӘжқҘдҫҝжңүжңӣи§ҒеҲ°жң¬йЎ№жҲҗжһңиҗҪең°еҲ°еёӮеңәеҢ–дә§е“ҒдёӯпјҢжҠҖжңҜиҠӮзӮ№зҡ„еә”з”ЁзӘҒз ҙ并дёҚд»…д»…жҳҜеҸ°з§Ҝз”өе’Ңдёүжҳҹ们йқ дёҖе·ұд№ӢеҠӣе®ҢжҲҗзҡ„пјҢеҗҢж ·д№ҹзҰ»дёҚејҖи®ҫи®ЎгҖҒи®ҫеӨҮгҖҒжқҗж–ҷгҖҒEDAеҺӮе•Ҷзҡ„е…ұеҗҢеҗҲдҪңпјҢд»Һж ҮеҮҶеҚ•е…ғеә“зҡ„е»әз«ӢеҲ°дә§зәҝе®һзҺ°еӨ§и§„жЁЎйҮҸдә§дёӯд»»дёҖдёҖдёӘдә§дёҡй“ҫзҺҜиҠӮзҡ„ж–ӯиЈӮеҸҜиғҪе°ұдјҡжҺЁиҝҹдёӢдёҖд»Је·Ҙиүәзҡ„дёҠеёӮж—¶й—ҙгҖӮиҝҷз§ҚзҺҜзҺҜзӣёжүЈзҡ„з ”еҸ‘з”ҹжҖҒеҜ№дәҺдёӯеӣҪйӣҶжҲҗз”өи·Ҝдә§дёҡзҡ„зӘҒз ҙе’ҢзӘҒеӣҙд№ҹжҳҜдёҖз§Қе·ЁеӨ§зҡ„жҢ‘жҲҳпјҢжү“йҖҡеә•еұӮжҠҖжңҜеҲ°дә§дёҡзҡ„й“ҫжқЎпјҢеҠ йҖҹдә§еӯҰз ”иһҚеҗҲгҖҒдёәдә§дёҡжіЁе…ҘжӣҙеӨҡзҡ„з§‘з ”еҠӣйҮҸгҖҒи®©жӣҙеӨҡз§‘з ”иҗҪең°дә§дёҡ并еҪўжҲҗдә§з ”д№Ӣй—ҙзҡ„иүҜжҖ§еҫӘзҺҜпјҢжҲ‘们зҡ„йӣҶжҲҗз”өи·Ҝдә§дёҡжүҚдјҡжӣҙеҠ еҝ«йҖҹзҡ„еҸ‘еұ•еЈ®еӨ§гҖӮ

и®әж–Үе…Ёж–Үй“ҫжҺҘпјҡ

https://ieeexplore.ieee.org/document/9241685

еҫҖжңҹй“ҫжҺҘ

| |||

| |||

| |||

|

е…іжіЁжӣҙеӨҡж Ҹзӣ®

в—Ҹ

в—Ҹ

в—Ҹ

в—Ҹ

в—Ҹ

в—Ҹ