本文介绍的是首例报道的在10nm以下先进节点运用CAT进行标准单元库检测的研究案例,集产业与研究领域的四大顶尖学府与企业,共同在3nm技术节点进行了多项测试,证明了CAT技术在10nm以下节点的实验性标准单元库的验证中仍然具有实用性,接下来一探究竟吧!

研究背景

新的技术突破凝聚着大量研究人员和产业人的辛勤汗水和灵感的碰撞,集成电路的先进技术节点更是需要大量的创新,从EDA、设备、材料到芯片设计、制造工艺和封装,都需要大量的技术创新。标准单元库*便是芯片设计中一个非常重要的基础环节。

新的技术突破凝聚着大量研究人员和产业人的辛勤汗水和灵感的碰撞,集成电路的先进技术节点更是需要大量的创新,从EDA、设备、材料到芯片设计、制造工艺和封装,都需要大量的技术创新。标准单元库*便是芯片设计中一个非常重要的基础环节。在标准单元库的设计中,研发团队需要“缩放加速装置”(scaling boosters)来重现在之前技术节点突破中的PPA(性能、功率与面积)制程红利。而10nm以下节点中,设计标准单元库的工作要比它们的前辈们复杂得多。CAT技术(Cell-aware Test)是进行节点缩进过程中的一种有效检测工具,它可执行晶体管级的测试用以识别标准单元的缺陷,此方法利用从模拟仿真导出的故障模型,同时使用与传统诊断相同的失败数据收集和诊断流程。

荷兰埃因霍芬理工大学、比利时IMEC、Cadence楷登电子和台湾国立清华大学的联合研究团队在IMEC的3nm CMOS工艺节点“iN5”*上对试验性质的“114单元库”*进行研究的过程中使用了CAT工具,这也是团队报道时首次在10nm以下的先进工艺节点中使用该技术。

该研究成果近期“Application of Cell-Aware Test on an Advanced 3nm CMOS Technology Library”为题于测试领域顶级会议《IEEE International Test Conference》的2019年度峰会上首次发表,并在2020年公开。来自前述四所研究机构和高校的Zhan Gao、Rogier Baert、Santosh Malagi等9人为本文共同作者。

*标准单元库:是IP库中最基本的一种。基于单元的设计的优点是对于一个给定的工艺,单元只需要设计和验证一次,而后就可以重复利用许多次,因此分摊了设计成本。从系统行为描述、逻辑综合、逻辑功能模拟,到时序分析、验证,直至版图设计中的自动布局、布线,都必须有一个内容丰富、功能完整的单元库的支持。另一方面,在自底向上的设计流程中,则是从单元库中一个个具体单元开始,逐步构成各级功能模块,直至整个系统。为了缩短设计过程并使设计自动化,基于单元的设计愈来愈受青睐。标准单元库在基于单元的设计中地位十分重要,是设计的基础,它为基于单元的设计流程的各个阶段提供支持,对设计的性能、功耗、面积和成品率至关重要。

*iN5:IMEC的技术节点之一,相当于集成电路制造中的3nm工艺。

*114单元库:为本研究团队所建立的标准单元库,主要应用于科学研究。

实验结论

研究团队在如下环节进行了CAT测试:

研究团队在如下环节进行了CAT测试:(1)基于寄生元件参数撷取的缺陷定位识别;(2)基于对单元库及其潜在缺陷精确模拟仿真的缺陷表征;

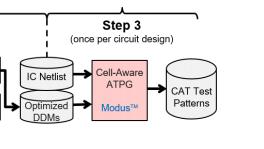

(3)基于iN5标准库,进行缺陷检测矩阵操作以优化后阶段的单元辨别自动测试图样产生*结果。

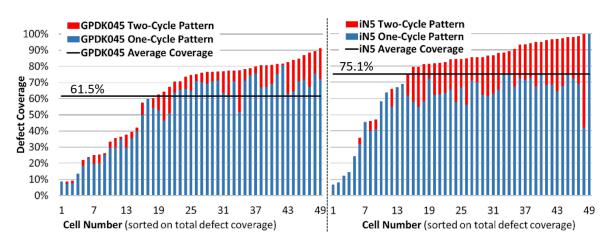

尽管增加了细胞的复杂性,实验结果表明CAT技术仍然有效,并且与45nm技术节点中功能相似的基本单元库相比,潜在的非等效缺陷位置、单元测试模式和缺陷数量没有显著变化。

*自动测试图样产:ATPG,Automatic test pattern generation, 是一种算法工具,能模拟出产生资料给制造出来后的数字电路作测试使用。ATPG工具能够在更短的时间内,产生更少的测试向量数,并获得更高的测试覆盖率,使得测试成本更低。

相关测试

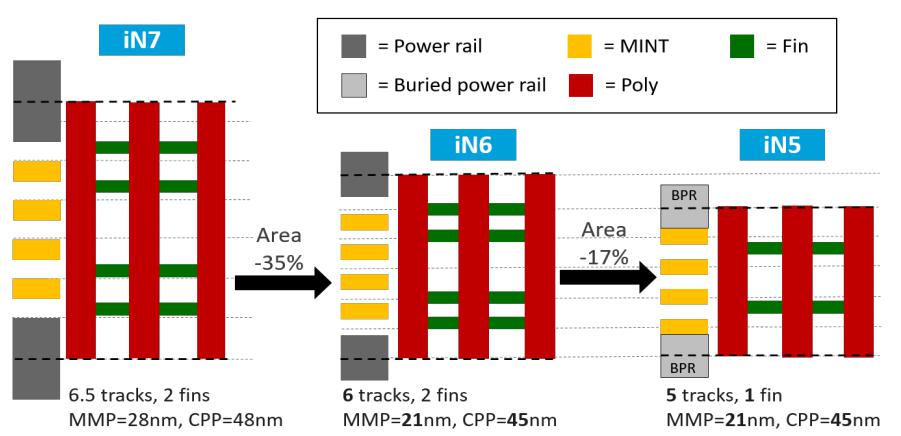

图为iN7节点到iN5节点的缩进过程示意图

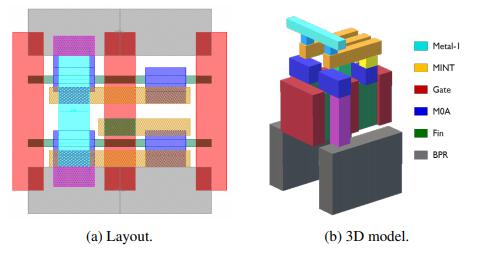

图为In5节点的标准单元“INVD”

滑动查看全部过程

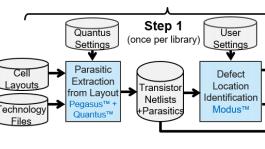

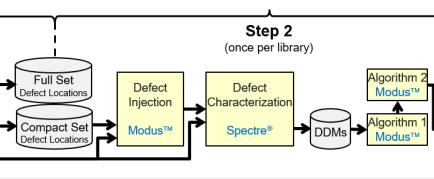

图(1) 缺陷定位识别过程;图(2) 缺陷表征过程;

图(3) ATPG过程

请滑动查看图2

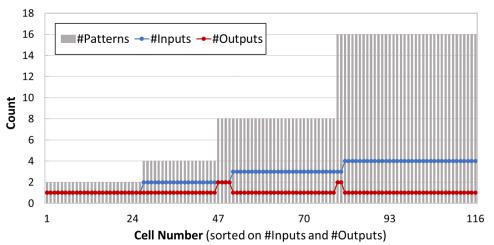

图(1):iN5单元库的输入、输出和模式的数量

图(2):iN5库单元中的短缺陷位置

GPDK045(Cadence的45nm单元库);

iN5单元的缺陷覆盖率对比

前景展望

本研究成果汇聚了领先的微电子技术研究机构IMEC、EDA巨头Cadence和顶尖学府埃因霍芬理工大学与台湾清华这四方的共同努力,集成电路先进制程取得技术突破的困难也可见一斑,其中之艰巨绝非一家企业、一所高校或一个高精尖技术的研究所能独立完成。EDA作为芯片设计的基础工具在我国集成电路产业链中属于薄弱环节,尚在发展的初期,相比世界先进水平有较大的差距。集成电路产业链之长,要追上国际先进水平,不仅需要产业链的通力合作实现新工艺突破,也需要企业与研究机构的产学研合作,从底层技术到产业应用形成一条完整的生态链,真正帮助中国IC产业屹立于世界。

本研究成果汇聚了领先的微电子技术研究机构IMEC、EDA巨头Cadence和顶尖学府埃因霍芬理工大学与台湾清华这四方的共同努力,集成电路先进制程取得技术突破的困难也可见一斑,其中之艰巨绝非一家企业、一所高校或一个高精尖技术的研究所能独立完成。EDA作为芯片设计的基础工具在我国集成电路产业链中属于薄弱环节,尚在发展的初期,相比世界先进水平有较大的差距。集成电路产业链之长,要追上国际先进水平,不仅需要产业链的通力合作实现新工艺突破,也需要企业与研究机构的产学研合作,从底层技术到产业应用形成一条完整的生态链,真正帮助中国IC产业屹立于世界。

论文全文链接:

https://ieeexplore.ieee.org/document/9000164

关注更多栏目

●

●

●

●

●

●

往期链接