栏目第三期为大家介绍的是西安电子科技大学微电子学院郝跃院士课题组的研究成果,团队以创新工艺实现增强型Si-GaN共源共栅晶体管的单片异质集成,异质集成工艺过程中无需晶圆键合设备或MOCVD等昂贵设备,可显著降低器件制备成本。

研究背景

熟悉半导体技术的人一定知道,氮化镓是第三代半导体材料的研究热点之一,在消费终端充电器、射频器件、5G基站等应用场景已经实现产业化;在可预见的未来,基于氮化镓材料的半导体器件在消费电子、汽车电子、机电控制、光伏产业和电源系统的各个细分领域中得到越来越多的应用。

电力电子器件更加需要常关态增强型氮化镓功率器件,但由于异质结二维电子气形成原因,一般的氮化镓器件主要是耗尽型的。一种可行的方案是由一个增强型硅晶体管与一个耗尽型氮化镓晶体管级联组成共源共栅增强型氮化镓器件,这种结构拥有稳定的正阈值电压并且与现有的栅驱动电路相兼容。此外,由于硅MOS结构的引入使得共源共栅氮化镓器件具有更大的与驱动电路兼容的栅压摆幅。然而,如何实现晶圆级单片集成Si-GaN共源共栅晶体管是一个十分困难的问题,因为这涉及到两种完全不同的半导体材料集成在同一片晶圆上。

在此背景下,国内团队在氮化镓晶体管与硅晶体管的异质集成工艺研究领域取得了重大进展:西安电子科技大学微电子学院郝跃院士研究团队的相关研究成果以《以转印与自对准刻蚀技术实现晶圆级增强型Si-GaN共源共栅晶体管的单片异质集成》(“Wafer-Scale Si-GaN Monolithic Integrated E-Mode Cascode FET Realized by Transfer Printing and Self-Aligned Etching Technolog”)为题发表在业界权威期刊《IEEE Transactions on Electron Devices》,张家祺博士和张苇杭博士为本论文的共同第一作者,张春福教授为论文的通讯作者。

基本特性

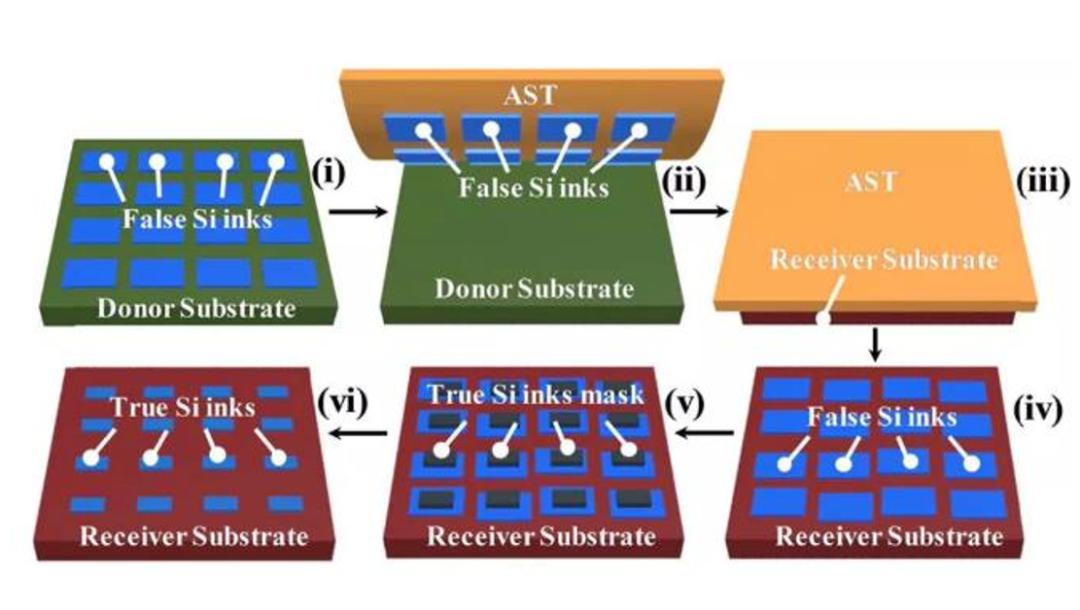

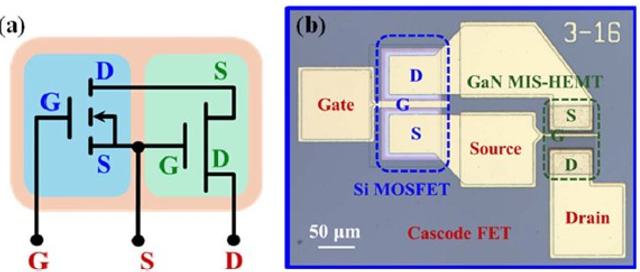

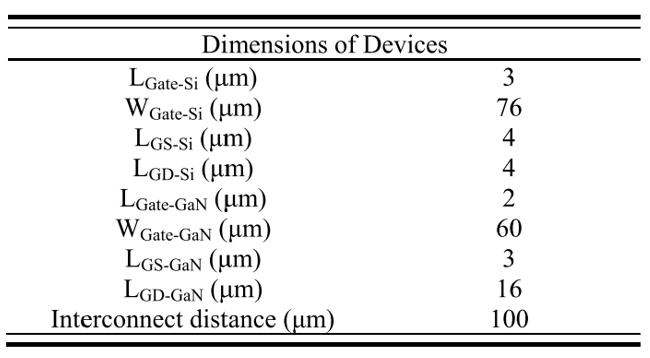

通过郝跃院士团队创新地提出了一种转印和自对准刻蚀方法(团队在《自然》杂志报告了这一工艺方法,将其命名为 “AST”),并实现了晶圆级的Si-GaN单片异质集成的共源共栅晶体管。通过转印和自对准刻蚀的新技术,使得硅器件与氮化镓器件的互连距离缩短至100μm以下,仅为传统键合线宽的5%。据估算,新型的共源共栅晶体管可以比传统键合工艺减少98.59%的寄生电感。Si-GaN单片异质集成的共源共栅晶体管的阈值电压被调制为2.1V,实现了增强型器件。该器件栅压摆幅在栅漏电低于10-5mA/mm的范围内达到了±18V。

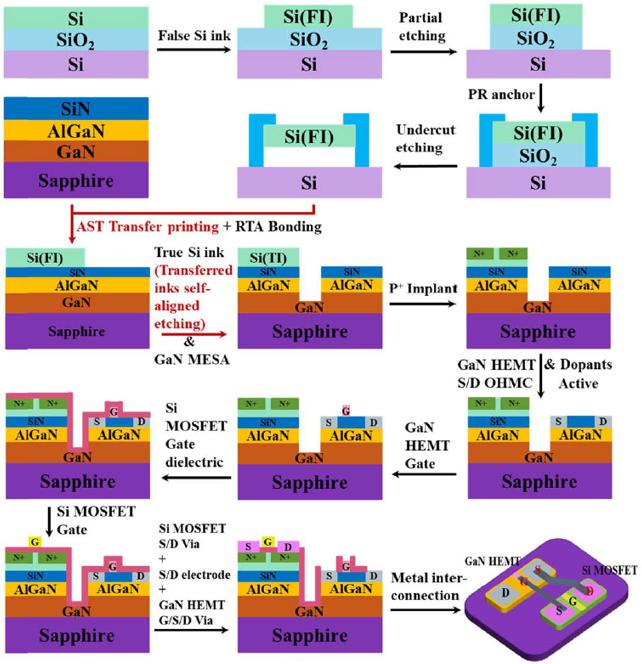

制备工艺

上图为Si-GaN共源共栅晶体管实现单片集成的工艺流程图

转印与自对准刻蚀技术的关键步骤示意图

部分测试结果

在本模块中,小编精选了部分晶圆形貌图和测试结果曲线图等。

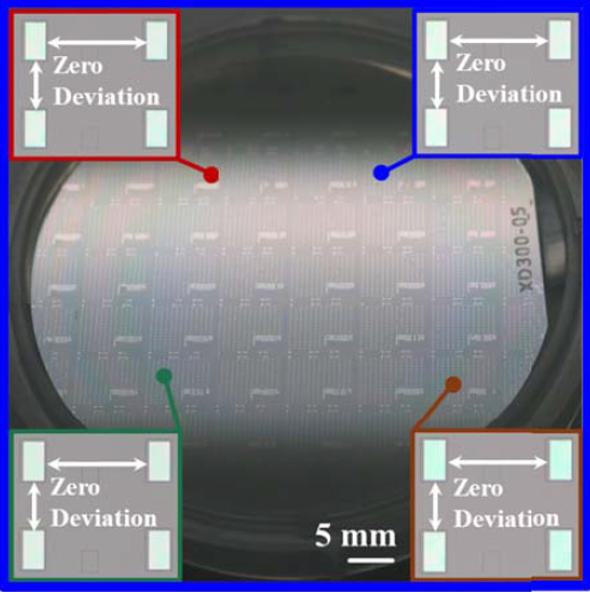

图为制备得到的Si-GaN晶圆

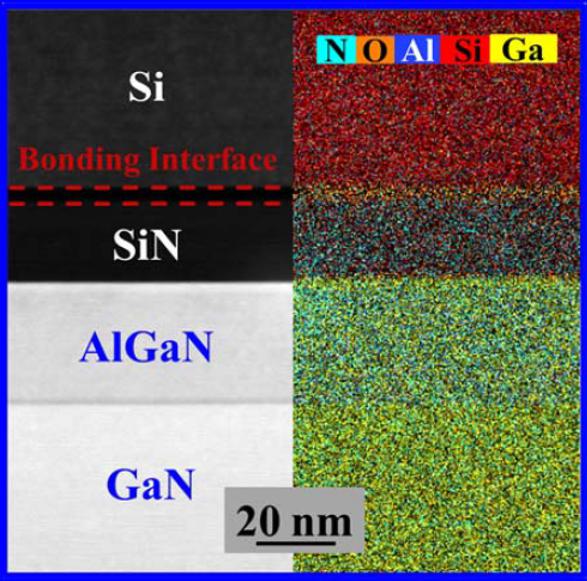

图(左)为异质结构横截面的TEM形貌像,图(右)为相应的EDX能谱图

图为Si/SiN键合界面的横截面TEM形貌像放大图

增强型共源共栅晶体管电路图及结构图

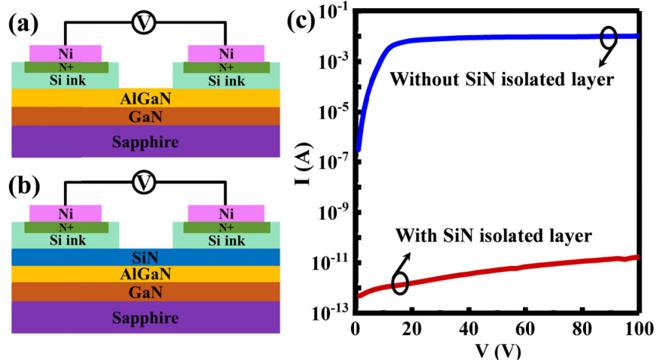

无/有SiN钝化层测试条件下的结构(左)以及对应I-V特征曲线(右)

本研究成果中Si-GaN器件的主要参数

应用前景

在研究团队经过大量器件测试和可靠性试验后,芯片之间的性能具有良好的一致性,这充分证明了转印和自对准刻蚀技术实现晶圆级单片集成共源共栅晶体管的巨大潜力和优势。通过采用转印与自对准刻蚀技术,有望实现多种材料的大规模异质集成并基于此制造功能多样化的器件和电路系统,避免了昂贵且复杂的材料异质共生技术或晶圆键合工艺,异质集成将成为芯片特征尺寸不断趋近物理极限背景之下突破摩尔定律的一条有效技术路径,我们也期待郝跃院士团队的研究成果能在其中发挥重大作用,助力中国芯片制造的技术升级和产业进步。

论文全文链接:

http://ieeexplore.ieee.org/document/9121694

AST工艺报告连接:

http://www.nature.com/articles/s41598-019-52235-0