Q1

жӮ¬иҮӮй’ҲжүҺwafer Pad жңүжҺҘи§ҰдёҚиүҜй—®йўҳпјҢwaferиҝӣиҝҮй«ҳжё©250В° bake еҗҺжҺҘи§ҰжҳҺжҳҫж”№е–„пјҢиҝҷжҳҜд»Җд№ҲеҺҹзҗҶпјҹеҗҢдёҖзүҮwaferгҖӮ

A1

еҸҜиғҪжҳҜйҮҚж–°жүҺй’ҲеҜјиҮҙдәҶеә”еҠӣйҮҠж”ҫпјҢwaferе№іж•ҙеәҰжӣҙеҘҪгҖӮ

Q2

еҷЁд»¶зҡ„CZ BuildжҳҜжҢҮд»Җд№ҲпјҹжҳҜд»Җд№Ҳзҡ„зј©еҶҷе•Ҡпјҹ

A2

CZжҳҜзү№еҫҒеҸӮж•° гҖӮ

Q3

е…ідәҺдёҺе®ўжҲ·еҲ¶е®ҡзҡ„дёҖдәӣиҙЁйҮҸзәҰе®ҡе“ҰпјҡдҫӢеҰӮжҲ‘е’Ңе®ўжҲ·зәҰе®ҡ3000ppmпјҢе®ўжҲ·еҸҚйҰҲзҡ„дёҚиүҜеӨ§жҰӮеңЁ1200ppmпјҲдҪҺдәҺspecпјүпјҢеҗ„дҪҚе…„ејҹе…¬еҸёжҳҜдјҡзӣҙжҺҘйҖҖз»ҷе®ўжҲ·д№Ҳпјҹе°ұжҳҜеңЁжңҖиҝ‘жҲ‘们еҸ‘зҺ°дёҖдёӘй—®йўҳе°ұжҳҜе®ўжҲ·еҸҚйҰҲзҡ„дёҚиүҜиҷҪ然ppmжҜ”иҫғдҪҺпјҢдҪҶжҳҜжҲ‘们йӘҢиҜҒдёӢжқҘзӣёеҪ“дёҖйғЁеҲҶеҸҜиғҪжҳҜжқҘжәҗе®ўжҲ·зҡ„иҮӘе·ұжөӢиҜ•е’Ңз„ҠжҺҘзҡ„еҺҹеӣ гҖӮе…ідәҺиҝҷдёҖзӮ№иҝҳжңүзӮ№иЎҘе……зҡ„жғіиҜ·ж•ҷдёҖдёӢпјҢе°ұжҳҜеҗ„дҪҚдёҺе®ўжҲ·зәҰе®ҡзҡ„ppmдёҖиҲ¬дјҡеңЁеӨҡе°‘пјҹ

A3

жӢҝеҮәеҲҶжһҗзҡ„иҜҒжҚ®пјҢиҜҙжҳҺжҳҜе®ўжҲ·зҡ„й—®йўҳе°ұиЎҢдәҶпјҢзәҰе®ҡзҡ„dppmдё»иҰҒзңӢеә”з”ЁпјҢиҝҳжңүдёҚеҗҢе®ўжҲ·иҰҒжұӮд№ҹжҳҜдёҚеҗҢзҡ„пјҢдёҖиҲ¬йғҪжҳҜfollowе®ўжҲ·зҡ„пјҢдҪҺдәҺзәҰе®ҡзҡ„ppmж•°жҚ®пјҢзӣҙжҺҘи·ҹе®ўжҲ·е…‘жҚўгҖӮи¶…иҝҮзәҰе®ҡзҡ„ppmж•°жҚ®пјҢжҠҪж ·еҲҶжһҗгҖӮ

Q4

Allegroз”»зҡ„дёӨеқ—дёҚеҗҢзүҲжң¬зҡ„жқҝеӯҗ пјҢиғҪеңЁallegroдёӯеҗҲ并еҗ—пјҹ

A4

дёӨдёӘAllegroз”»зҡ„жқҝеӯҗжҳҜеҸҜд»ҘеҗҲ并еҲ°дёҖиө·зҡ„гҖӮ е°ұжҳҜжҠҠBoard1 зҡ„placementе’Ңsubdrawing еҲҶеҲ«жӢ·иҙқеҲ°board2йҮҢгҖӮ еӣ дёәеҫҲеӨҡдҪҚеҸ·дјҡйҮҚеӨҚпјҢжүҖд»ҘеңЁжӢ·иҙқд№ӢеүҚпјҢе…ҲrenameпјҢжҠҠBoard1зҡ„дҪҚеҸ·еҲҶеҲ°дёҖдёӘдёҚеҸҜиғҪйҮҚеӨҚж•°еӯ—еҢәй—ҙгҖӮ жҜ”еҰӮRд»ҺR10000ејҖе§ӢгҖӮ

Q5

е…ідәҺflip chipе·Ҙиүәзҡ„з ·еҢ–й•“иҠҜзүҮ DecapзЎ®и®ӨиҠҜзүҮиЎЁйқўжҚҹеӨұзӮ№жңүд»Җд№ҲеҘҪзҡ„ж–№жЎҲпјҹиҠҜзүҮе°әеҜёжңүзӮ№е°ҸпјҢжҳҜ1mm*1mmзҡ„гҖӮ

A5

зЈЁеҺ»еҹәжқҝжҲ–жЎҶжһ¶пјҢзЈЁеҲ°bumpдҪҚзҪ®пјҢ然еҗҺеҢ–еӯҰи…җиҡҖеҺ»жҺүmolding гҖӮ

Q6

ж”№дәҶи®ҫи®Ўleakageд»Һ100uAеҸҳжҲҗ10uAпјҢжҳҜдёҚжҳҜеҸҳе°ҸдәҶпјҢEOSзҡ„йЈҺйҷ©д№ҹдјҡеҸҳдҪҺпјҢдёҡз•Ңжңүиҝҷз§Қз ”з©¶еҗ—пјҹеҜ№еә”JEDECе“ӘдёӘж ҮеҮҶпјҹ

A6

еҜ№еә”JEP174гҖӮ

Q7

uHASTжҳҜ130еәҰпјҢ85ж№ҝеәҰпјҢ96hпјҢTHTжҳҜ85еәҰпјҢ85ж№ҝеәҰпјҢ1000е°Ҹж—¶пјҢиҝҷдёӨдёӘеҸҜд»Ҙдә’зӣёжӣҝжҚўеҗ—пјҹжҜ”еҰӮдёәдәҶдёҚеҒҡ1000е°Ҹж—¶иҝҷд№Ҳй•ҝж—¶й—ҙпјҢж”№еҒҡuhastжҳҜдёҚжҳҜд№ҹжҳҜдёҖж ·зҡ„пјҹ

A7

жҳҜзҡ„гҖӮ

Q8

HTOL LTOLи®ҫи®Ўpattern жңүд»Җд№ҲиҰҒжіЁж„Ҹзҡ„еҗ—пјҢи·‘зҡ„ж—¶еҖҷеҠҹиҖ—жңүиҰҒжұӮдёҚпјҢжҳҜдёҚжҳҜиҠҜзүҮеҠЁиө·жқҘе°ұеҸҜд»ҘпјҢеҠҹиҖ—еә”иҜҘжІЎжңүиҰҒжұӮеҗ§пјҹ

A8

з”ЁDFTеҗ‘йҮҸи·‘еҗ§пјҢе°ҪйҮҸи®©жүҖжңүз”өи·ҜйғҪеҠЁиө·жқҘпјҢиҝҳжңүжіЁж„ҸдёҚеҗҢpatternзҡ„еҠҹиҖ—дёҚиҰҒе·®ејӮеӨӘеӨ§пјҢе…Қеҫ—йғЁеҲҶpatternз»“жё©еӨӘдҪҺпјҢйғЁеҲҶеҸҲиҝҮй«ҳгҖӮ

Q9

иҪҰ规зә§е’Ңе·Ҙдёҡзә§иҠҜзүҮйӘҢиҜҒзҡ„еҢәеҲ«еңЁе“ӘйҮҢпјҹ

A9

дё»иҰҒжҳҜй«ҳдҪҺжё©зҺҜеўғпјҢиҪҰ规зҡ„еҸӮиҖғAEC-Q100е’Ң101ж ҮеҮҶпјҢе·Ҙдёҡзә§еҸӮиҖғJESD47ж ҮеҮҶгҖӮ

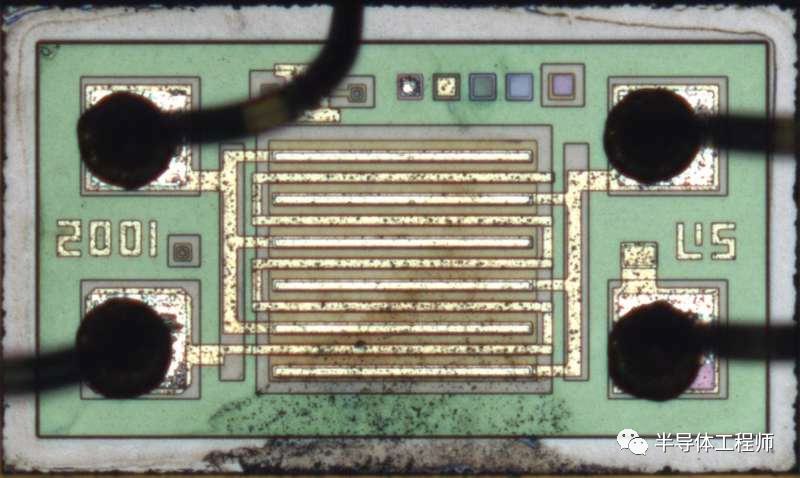

Q10

жңүеҜ№жЁЎжӢҹиҠҜзүҮжҜ”иҫғзҶҹзҡ„еҗ—пјҹеё®еҝҷзңӢдёӢжҳҜе“Ә家зҡ„иҠҜзүҮгҖӮ

A10

жҳҜдёҖдёӘmosз®ЎгҖӮ

Q11

иЎ°еҮҸеҷЁжҳҜеҗҰеҸҜд»Ҙж”ҫеңЁ50欧е§ҶеҢ№й…Қз”өи·ҜдёҚеҘҪзҡ„жҺҘеӨҙз«ҜпјҢз”ЁдәҺж”№е–„йҳ»жҠ—еҢ№й…Қ? зңӢзҪ‘еҲҶзҡ„TDR еӣҫзЎ®е®һжҳҜжңүж”№е–„пјҢдҪҶжҳҜдёҚзЎ®е®ҡжҳҜдёҚжҳҜеӣ дёәеҸҚе°„дҝЎеҸ·иў«иЎ°еҮҸдәҶпјҢжүҖд»ҘTDRжҳҫзӨәжңүж”№е–„гҖӮ

A11

йӮЈиӮҜе®ҡжҳҜеӣ дёәеҠ дәҶиЎ°еҮҸеҷЁжүҚжҳҫеҫ—TDRзңӢдёҠеҺ»еҸҳејұдәҶе•ҠпјҢжү“дёӘжҜ”ж–№пјҢеҒҮеҰӮз”өи·ҜеӨ„дәҺжһҒз«ҜдёҚеҢ№й…ҚзҠ¶жҖҒж—¶дҝЎеҸ·ж— жі•з©ҝйҖҸеҢ№й…Қз”өи·ҜеӨ§йғЁеҲҶиў«еҸҚе°„пјҢеўһеҠ дәҶиЎ°еҮҸеҷЁеҸӘдјҡи®©йӮЈдёҖз«ҜеҸҚе°„жҳҫеҫ—еҸҳж”№е–„е…¶е®һдҝЎеҸ·иҝҳжҳҜжІЎз©ҝйҖҸз”өи·ҜгҖӮ

Q12

иҖғиҷ‘иҖҒеҢ–иҜ•йӘҢпјҢдёҖйў—иҠҜзүҮпјҢе®Ңж•ҙе·ҘдҪң25PINпјҢеҜ№еӨ–еә”з”Ё21pinгҖӮиҖҒеҢ–иҰҒиҖғиҷ‘21иҝҳжҳҜ25пјҹ

A12

жІЎжңүз»қеҜ№е®ҡд№үгҖӮжҖ»дҪ“з”ЁиҰҶзӣ–зҺҮе®Ңж•ҙзҡ„гҖӮиҷҪ然еҸҜд»Ҙз”Ё21pinзҡ„иҖҒеҢ–пјҢе…¶е®ғеҮ дёӘиҫ“е…ҘpinжӮ¬з©әжҲ–жҺҘеӣәе®ҡз”өе№ігҖӮдҪҶжҳҜд»ҺжЈҖжҹҘдёҖйў—иҠҜзүҮе®Ңж•ҙзҡ„и®ҫи®Ўз ”еҸ‘еҸҜйқ жҖ§жқҘи®ІпјҢеҒҡ25pinжҳҜеҗҲзҗҶзҡ„пјҢеҸҜд»ҘдёәжңӘжқҘзҡ„зүҲжң¬е®Ңж•ҙе·ҘдҪңжҸҗдҫӣдҫқжҚ®гҖӮ

жқҘжәҗ:дёҠжө·еӯЈдё°з”өеӯҗ

жҠ•зЁҝ/жҺЁе№ҝ/е№ҝе‘Ҡ/е…ҘзҫӨ/иөһеҠ©/иҪ¬еҸ‘ е’ЁиҜўictest1