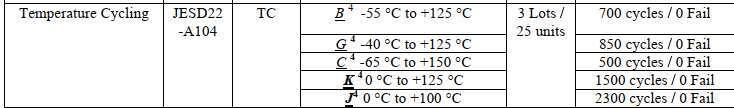

Q1

请问TC循环多少cycle,怎么选呢?有标准依据吗?

A1

Q2

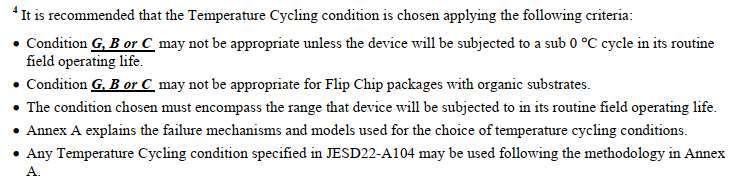

这个floor life怎么理解?拆包,还是密封抽真空条件?

A2

当然是拆包后。

Q3

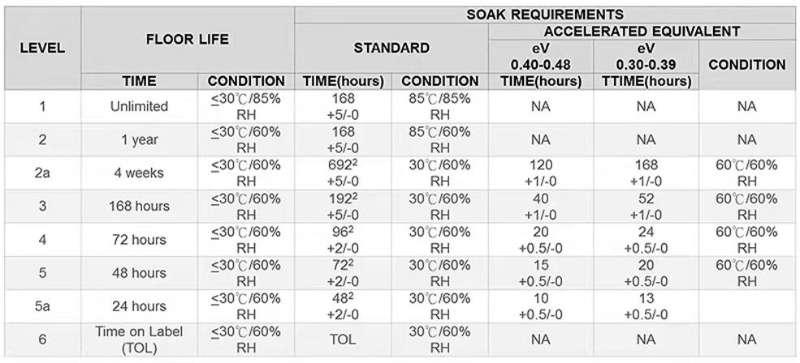

请教一下,封装之后做了precon+TCT500后的切片,这种程度的void可以接受吗,测试都是PASS的?

A3

bump之后先看x-ray结果判定void是否超标。如果正常那么还要注意bump COP是否在spec范围内。

Q4

如上同批料前后各切了8ea,之前的bump的void比例4/48,之后的是10/56。再请教一下,TC会产生void吗?

A4

其实从你说的结果看如果void大小差不多的话不能说明TC对bump产生了很大影响。TC容易引起crack/separation,不太容易引起void. 我对可靠性不太了解,但我理解HTOL也许更容易引起 Void吧,柯肯德尔效应…而且从照片看我更倾向于是研磨的问题。

Q5

scan shmoo 哪位知道这是什么原因 timing?电压drop?正常电压1.2v 为什么1v更容易pass?

A5

error map,waveform,pin margin都看看,如果是solid failure,也有可能scan setup stage有问题,即scan mode没进去,另外板子电容够不够,会不会scan跑起来,电源响应慢,电压瞬间降到低于reset threshold,导致scan模式退出。

Q6

请教各位,芯片的保质期通常应该定多久?

A6

这个看产品形态,一般铝pad,铝层没有严重污染的话,封装有关性能影响不大。一般铝pad的wafer,铝层没有严重污染的话,放个几年,封装有关性能影响不大。继续封装时看。

Q7

所谓芯片保质期(180/360/450天),是基于功能、性能影响的评估吗?

A7

主要看pad,良率和可靠性风险。

Q8

消费类芯片过两次IR,温度220℃,时间就是SMT正常profile,约6分钟,做这个条件过两次IR会不会对产品的寿命和性能有严重的影响,导致SMT无法正常生产和客户端的使用寿命减少和品质隐患?

A8

一般返工只能做一次IR;通常总IR次数不能超过3次。

Q9

求教一下各位:三颗die合封在一起有什么需要注意的事项?一颗主控两颗mem?

A9

这要看要封什么形式,什么尺寸,,主控Pad分布以及和KGD的连线,联系好对囗的封测厂,要一要design rule,打线的,那得根据尺寸看两颗mem的和主片的叠放情况,KGD买现成的,那就视互相打线情况,对主控的Pad进行调整,早点找封测做评估。

Q10

请问一下:是否有好的方法将已封装好的芯片,取下来,重新进行COB?

A10

Decap,需要取裸die出来,装在另外的EVB上,取die的时候,如果长时间的药水会破坏芯片,吃出来,拔掉线,直接打是有可能的,但是良率比较低,而且焊线如果是Au的,药水都吃不掉,线还得自己拔,包括金线也得自己拔,记得带着焊球,不然不好打线,不过给季丰,直接要结果就行。

Q11

请教一下各位,用于可靠性测试(比如HTOL/HAST)的socket的寿命一般是怎么考虑的?

A11

htol的厂商一般都说1万小时左右,不过这个在不变形,电性能正常的情况下一直都能用,我就有一款SOP8封装的,用了5万小时,socket没坏几个,到是电路板上的其他元器件不是很好了。跟功耗(发热)和电路复杂度也有关。功耗大,socket寿命相对就短;电路复杂,能稳定运行的时间也会比较短,比如有各种相对大功耗的PHY BIST在切换,后来就担心复杂电路跑不顺,也不敢用了。这种一般5000小时左右。

Q12

各位,这种管腿氧化,一般会是电镀导致的吗?产品是近期加工的?

A12

很大的可能。(电镀处理液没有清洗干净,经过后面高温烘烤,或暴露空气中氧化了)5%的甲基磺酸,浸泡几分钟后烘干就行了。或者EDX看看这个变色的到底有些啥元素,如果是BGA 球变色,建议Ionography测试看看是否flux residue。

Q13

请问芯片spec结温写的150℃ATE测试的话,如果时间很短是否也要按照150°来进行高温测试呢?

A13

如果对外的spec里写了节温150,说明要保证die在这个温度能工作,如你说ate测试时间很短,这就抛出了die自身发热的因素,所以150的高温是有必要的。

Q14

大家好,想咨询一下,如果表贴器件在封装阶段(电镀前)过两次回流焊,对产品的性能和终端的上机焊接会产生哪些影响呢?

A14

考核是3次reflow,你在线做了2次,就只留了1次给终端客户了。

Q15

大家好,请问群里有大神知道关于存储芯片的MTBF里面激活能一般取多少吗?

A15

没有特定的失效模式就选0.7。

Q16

请问大家有了解和做过wafer level burn in的同仁,帮忙提供一些参考意见?

A16

建议看一下JESD241文件。

Q17

请问芯片的真空包装保存期限根据什么得到的?如何计算芯片存储的保存期限?

A17

大家讲的保质期,都是指shelf life。从两个层面说吧,最早的wafer 的shelf life是从raw wafer (substrate)来的,有的是一年,有的vendor是给两年,这个主要是考量存放久了会有杂质析出。后来很多客户也都基于这个concept问成品的wafer能放多久,因为8他们经常会遇到crystal的问题,后来他们也说一年两年的,实际上成品的wafer主要考虑的是后端工艺带来的hf残留和保存环境带来的影响,并且每家包材都是不一样的(透气率),且放的干燥剂克数也不一样,所以通过标准算出来一个数字作为参考。对于特殊的产品譬如memory,也有可能因为长时间的存放会导致reference cell 的trimming value变化,但主要的还是看pad是不是有问题,有问题会影响后续打线,部分还有可靠性风险。

来源:上海季丰电子

分享二维码到朋友圈免费为您发文章一篇

欢迎各公众号,媒体转载

投稿/推广/合作/入群/赞助/转发 请加微信13488683602