个人简介

刘视远,北京大学集成电路学院博士研究生。2020年毕业于华中科技大学光学与电子信息学院。目前主要研究高性能二维过渡金属硫族化合物晶体管器件。

背景介绍

过去的五十年间,晶体管的尺寸按照摩尔定律不断缩小,以实现功耗-性能-面积的进步。短沟道效应是硅基场效应晶体管尺寸缩小面临的重要挑战。为了实现对沟道更好的控制,同时提升器件性能和集成度,围栅(GAA)堆叠纳米片(stacked nanosheet)器件和垂直堆叠互补型场效应晶体管(CFET)被认为是未来极具潜力的器件形态。当前先进的工艺正从FinFET转向GAA堆叠纳米片结构,纳米片的结构也常被用做构建未来技术节点器件的结构单元:如n/p更加紧密的Fork Sheet结构;或将n型和p型纳米片垂直堆叠到一起的CFET结构,减小工艺单元的中心间距,极大的缩小了CMOS单元面积。为进一步提升集成密度和降低成本,必须持续缩小栅极长度,因此沟道厚度也需要同步减薄以维持栅控能力。而三维半导体材料随着厚度的减薄,会受到量子限域效应和更强散射的影响,其载流子迁移率迅速降低。过渡金属硫族化合物(TMDs)如二硫化钼(MoS2)和二硒化钨(WSe2)等二维材料,载流子被限制在原子层厚度的区域中,在小于1 nm的体厚度下仍具有合适的带隙和迁移率,并可通过CVD或MOCVD的方法低成本、大面积制备,是理想的沟道材料。已有的研究通过优化材料生长、界面、接触等方式提高了平面TMDs沟道器件的性能,然而对垂直堆叠沟道器件的研究却很少。目前所报道的TMDs堆叠纳米片晶体管主要基于机械剥离的薄片,需要精准的对齐转移方法,限制了器件的规模制备。

本工作中,通过大面积CVD生长的MoS2制备了双层沟道的堆叠围栅纳米片器件,器件性能相对与单层沟道具有大于两倍的提升,并分析了数百个器件的性能统计分布规律。此外还制备了单原子层MoS2/WSe2垂直堆叠互补型场效应晶体管CFET,实现反相器逻辑功能。

论文名称:

Demonstration of Vertically-stacked CVD Monolayer Channels: MoS2 Nanosheets GAA-FET with Ion>700 µA/µm and MoS2/WSe2 CFET

论文链接:https://ieeexplore.ieee.org/abstract/document/9720533

为本课题组2021年发表在IEDM会议上的工作。

二硫化钼堆叠围栅纳米片器件

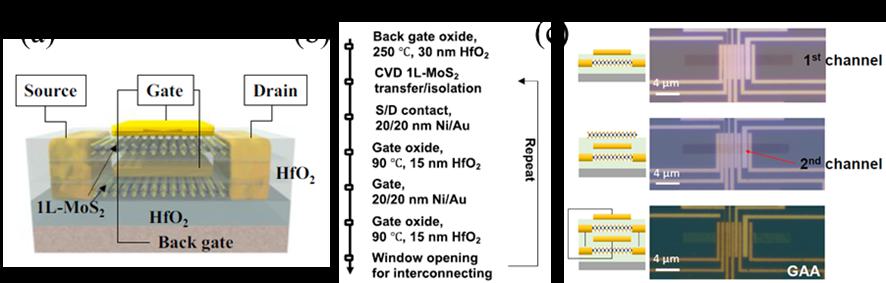

图一为本工作中器件结构示意图、工艺流程图及不同器件工艺过程下的光学显微镜照片,通过层层堆叠的介质层和金属栅层,以及厚度小于1 nm的MoS2沟道层,完成了器件制备。

图 一 (a) 堆叠围栅纳米片器件结构及工艺流程 (b) 工艺流程中的器件的显微镜照片。

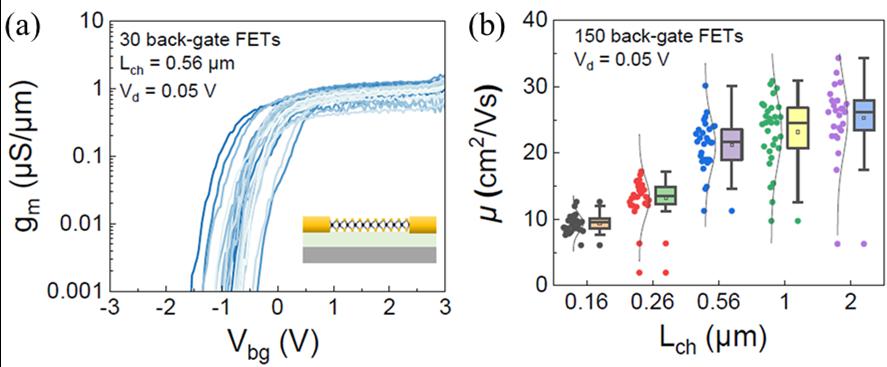

图二是MoS2材料的基本性能,分别为30个沟长为0.56 μm的背栅器件在Vd = 0.05 V下的跨导曲线及150个不同沟长背栅器件的迁移率分布图,提取出的载流子迁移率高达30 cm2 V-1 s-1。基于此均匀的高质量薄膜,制备了上百个堆叠纳米片器件。

图 二 (a) 30个沟长为0.5 μm的背栅MoS2晶体管在,Vd = 0.05 V时的跨导曲线和 (b) 150个不同沟长背栅器件的载流子迁移率分布图。

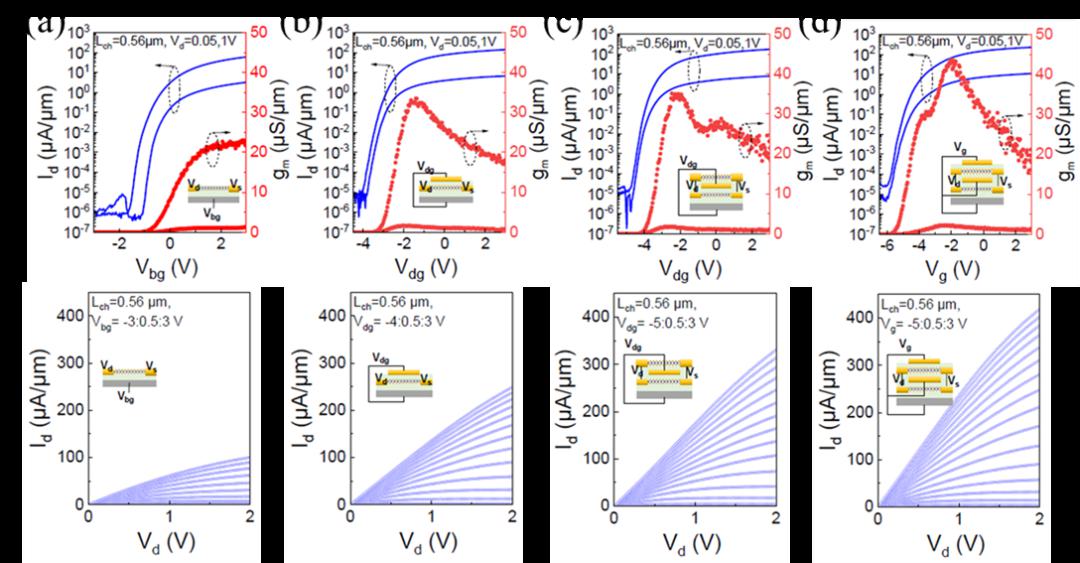

为了更好地评估器件性能,对器件制备过程中的每一步进行了电学测试,下图中分别是0.56 μm沟长下单层沟道背栅晶体管(1Ch_BG)、单层沟道双栅晶体管(1Ch_DG)、双层沟道双栅晶体管(2Ch_DG)和双层沟道环栅晶体管(2Ch_GAA)的转移特性曲线和输出特性曲线。

单层背栅晶体管具有>10^7的较大开关比,在Vd = 1 V时的最大gm为~22 μS/μm,在Vd = 2 V和Vbg = 3 V时的开态电流为~100 μA/μm。顶栅沉积后,通过对顶栅和背栅施加相同的偏压实现了双栅晶体管。双栅MoS2晶体管在Vd = 1 V时阈值电压负移,最大gm为~33.5 μS/μm,相对于背栅器件提高了45%。在Vd = 2 V和Vdg = 3 V时,双栅MoS2晶体管的最大开态电流达到249 μA/μm。双栅结构的双层沟道晶体管在Vd = 1 V时有两个gm峰,最大峰值为37 μS/μm,证明两个MoS2沟道都参与了载流子输运。2Ch_DG器件在Vd = 2 V和Vdg = 3 V时,最大开态电流为~330 μA/μm。将各层栅极相互连接并施加相同的偏压,在Vd = 1 V时,GAA晶体管的最大gm为~45 μS/μm,性能相对初始背栅晶体管有两倍以上的提升,在Vd= 2 V、Vg = 3 V时,2Ch_GAA器件的开态电流可达420 μA/μm。

图 三 (a)-(d) 单层沟道背栅晶体管、单层沟道双栅晶体管、双层沟道双栅晶体管和双层沟道环栅晶体管的转移特性曲线和输出特性曲线。

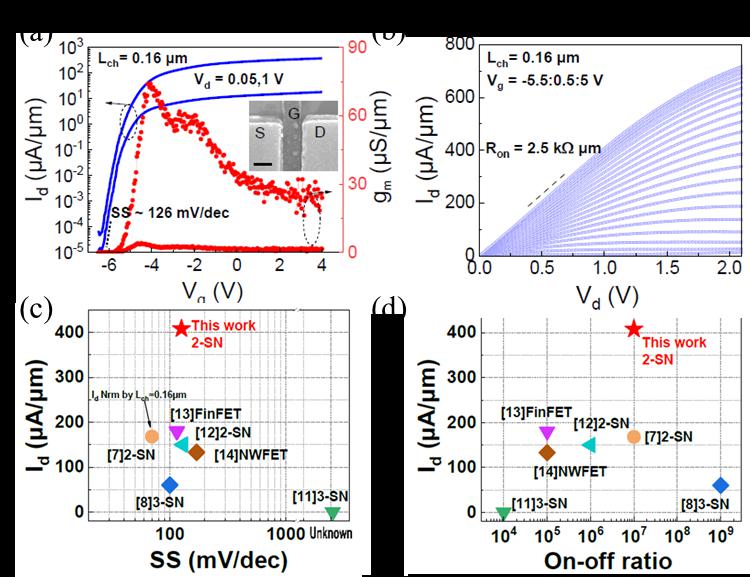

器件性能的提高主要来自四个方面:一是GAA结构增加了有效栅电容提高了载流子密度;二是有效表面钝化降低了散射;三是双层增加了载流子的输运路径;四是环栅结构实现了器件阈值负移。沟长缩短至Lch = 0.16 μm时,实现了高性能双层沟道堆叠围栅纳米片器件,如下图所示,Vd = 1 V时,最大gm为~75 μS/μm,SS低至~126 mV/dec,开关比为~10^7;在Vd = 1 V时,开态电流为~408 μA/μm,Vd = 2 V时输出电流~700 μA/μm,Ron为~2.5 kΩ μm,通过传输线法提取接触电阻Rc为~0.77 kΩ μm。图(d) (e)对基于TMDs的堆叠纳米片或3D结构器件的性能进行了对比评估,表明本文中的器件在开态电流方面比其他器件更有优势。

图 四 (a)-(b) 沟长为0.16 μm的双层堆叠纳米片器件的转移特性曲线和输出特性曲线;(d) 基于TMDs沟道的三维结构器件在Vd = 1V时的开态电流和亚阈值摆幅对比;(e) 基于TMDs沟道的三维结构器件在Vd = 1V时的开态电流和开关比对比。

二硫化钼/二硒化钨垂直堆叠互补型场效应晶体管

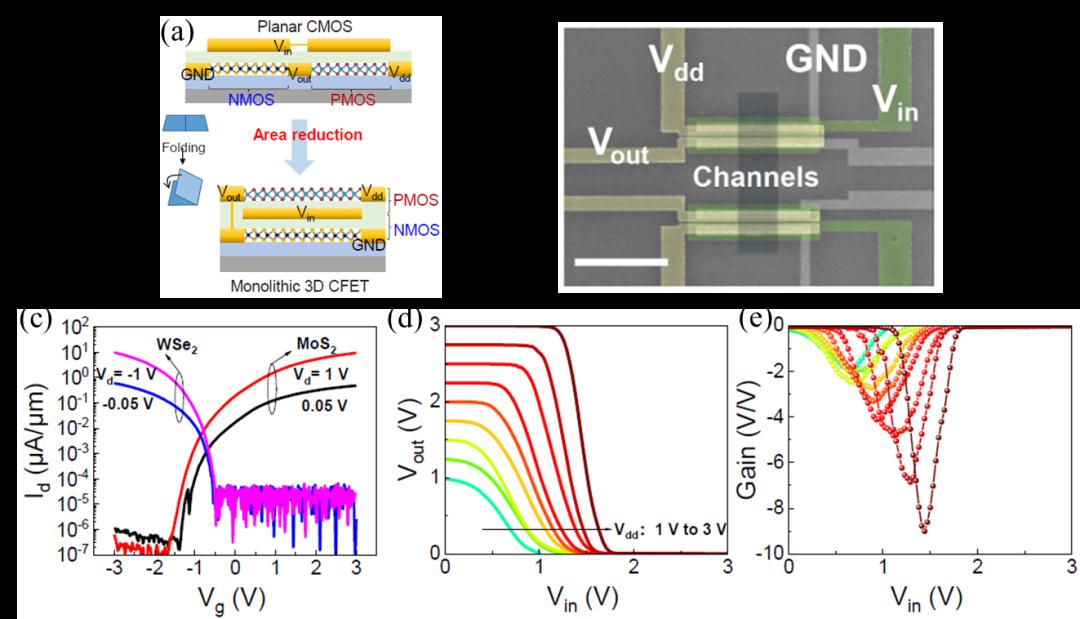

此外,本文首次实现了基于CVD生长材料的三维堆叠CFET。下图为MoS2/WSe2 CFET器件示意图和SEM图像。CFET的制造过程与堆叠围栅纳米片器件相似,但用p型沟道WSe2取代了上层MoS2沟道。CFET的两个沟道共用一个金属栅极,因此减少了大约一半的面积占用。MoS2和WSe2 FET的转移特性如图(c)所示。图(d) (e)为堆叠型CFET反相器在不同Vdd时的电压转移特性曲线,Vdd = 3 V时的最大增益为~9 V/V。CFET逻辑反相器实现了0至Vdd的全摆幅输出和轨到轨转移特性关系,有望实现更大规模互连集成。

图 五 (a)-(b) MoS2/WSe2 CFET器件示意图和SEM图像;(c) MoS2和WSe2晶体管转移特性曲线;(d) CFET反相器的电压转移特性曲线及;(e) 器件的电压增益曲线。

总结

本工作展示了基于单层二硫化钼的双堆叠围栅纳米片器件,在Vd = 1V实现了超过400 μA/μm及Vd = 2V下700 μA/μm开态电流,该结果远超同类器件的水平;通过上百器件的统计分析,展示了堆叠环栅纳米片器件由三维集成和尺寸缩小带来的性能提升;该工作还首次报道了亚1 nm沟道厚度的二硫化钼/二硒化钨垂直堆叠互补型场效应晶体管,实现逻辑反相器功能,为二维沟道材料在三维单片集成中的应用提供了新的可能。

来源:芯系清华

分享二维码到朋友圈免费为您发文章一篇

欢迎各公众号,媒体转载

投稿/推广/合作/入群/赞助/转发 请加微信13488683602