Q1

请教下,HTOL JEDEC,bias一方面要求bias调节到最小节温,一方面又要求最大的工作电压,这两者怎么理解?

A

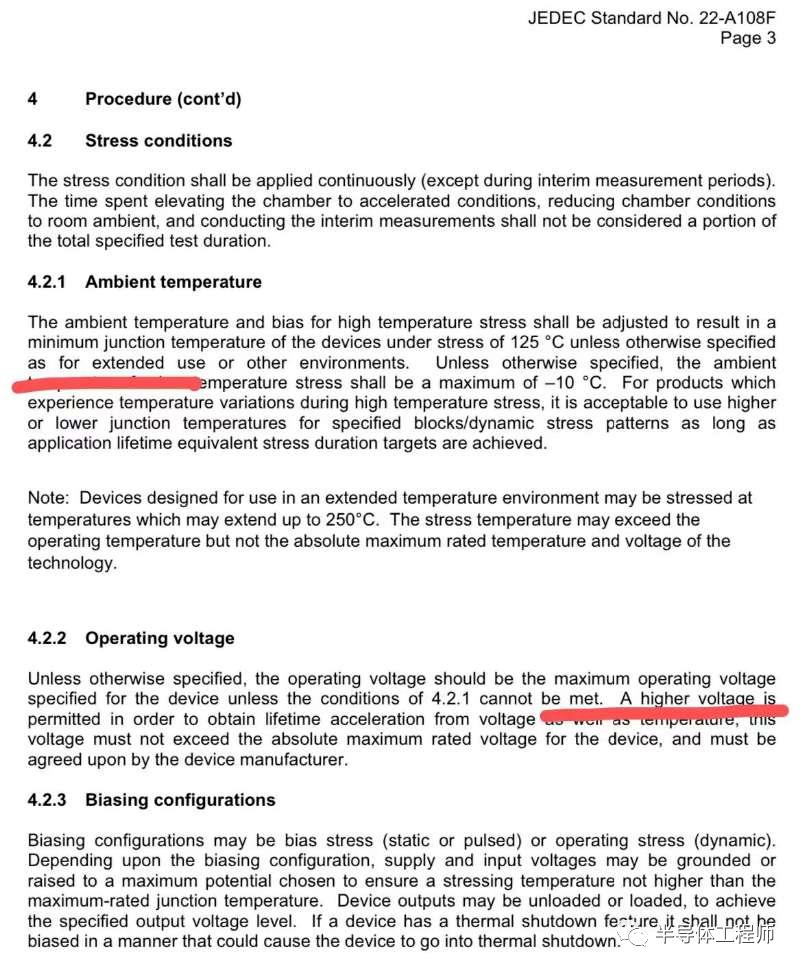

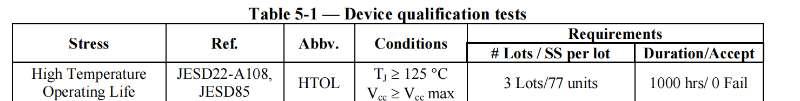

图片里面第一个标红的地方的意思是:在环境温度和偏压的综合应力下,让结温达到最低测试要求的125度,并不是结温要求越低越好。不能一开始环境温度就要到125度,否则对于功耗比较大的芯片,结温肯定会超过125度了,当然,如果测试spec要求超过在125度结温下测试的话,那就另当别论了。图片上第二个标红的地方,是当觉得比如1.1倍电压加速效果如果不好的话,可以采用更高电压比如1.2倍下加速,这个时候,通过调整环境温度,结温依然可以保持在125度。JESD47里面对HTOL测试时结温有个125度的最低要求。

Q2

各位请教个问题,我们一根高速数据线与邻近的地线,通过x-ray 并没有连在一起,但是ATE 测试short fail,抓热点的位置也在两个线最近的距离处。这个怎么理解?

A

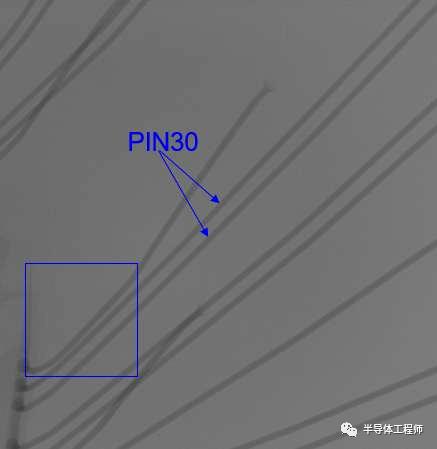

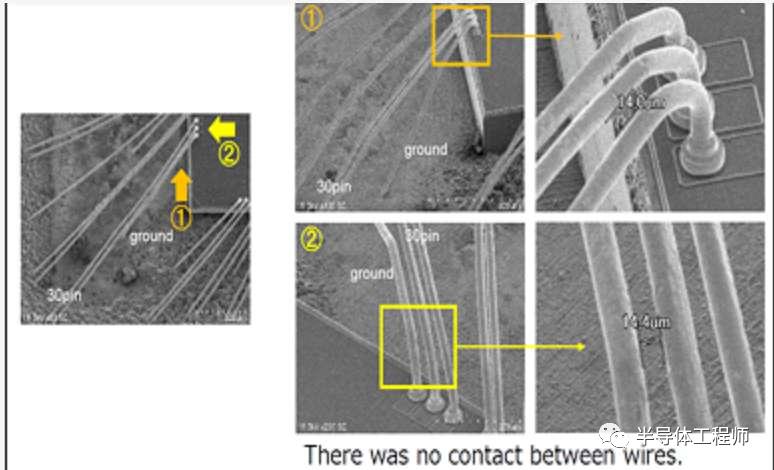

一种可能性是两者之间的mold compound碳化了,导电但是通过X-ray看不到。对这种情况我觉得热点的位置应该是值得相信的。或者其他Xray看不到的导电物质。还有就是,Xray看到的情况跟是实际情况是有一定区别的,毕竟那只是衬度的不同。两者看起来没有接触不能证明实际没有。还要看Xray的分辨率和使用条件。这种情况如果直流确实有短路,而且抓到了热点,那就可以通过物理隔离,decap xsection等找到短路点。

Q3

如图是上述 decap后的x-ray 照片,这时用IV 看还是对地short?

A

正常线距要求一倍以上的距离,你这20u-30um不符合要求,后期无论是可靠性还是客户使用会有短路风险。

Q4

打线水平间距、垂直间距,行业标准是多少?

A

线间距最低1个线径,一般要2个线径以上比较好。

Q5

请教:一个芯片,管脚有110uA的漏电。在咱们季丰做了热成像,中间亮的部分是电阻区。问题是,在芯片右下角边缘有亮,这个是否常见或正常?

A

衬底漏电了啊,这个位置想确认的话可以考虑取die,从背面再看一遍。

Q6

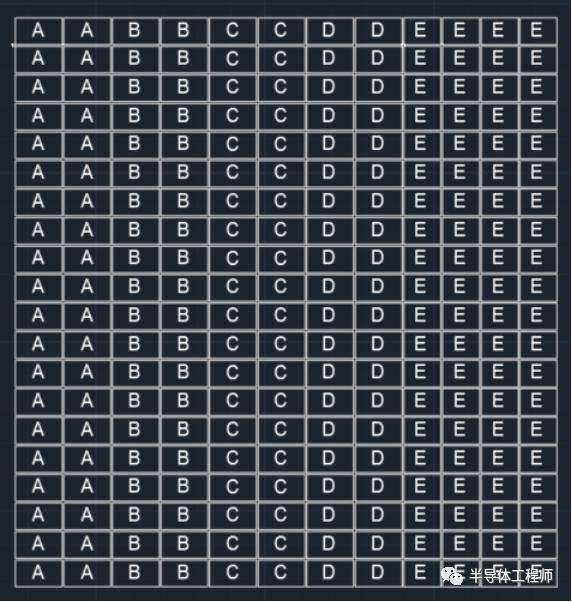

下图是晶圆排布,左面ABCD区域Y方向芯片之间space是70um,E区域变成60um,在X方向切割时,可以一刀划到底吗,光学对位会不会存在问题?ABCD四种芯片高度都是985,E高度995um

A

全部按照60um切割道切就可以了。

Q7

光学对位呢,从e区到abcd区域,会不会因为图像识别问题频繁报警?

A

不会,MPW wafer的切割跟single die 会有不同的管控方式。

来源:上海季丰电子

分享二维码到朋友圈免费为您发文章一篇

欢迎各公众号,媒体转载

投稿/推广/合作/入群/赞助/转发 请加微信13488683602