本期分享者复旦大学微电子学院的马顺利老师。

马顺利,复旦大学微电子学院青年副研究员。本科毕业于上海交通大学微电子学与固体电子学系,博士毕业于复旦大学。博士期间,在新加坡南洋理工VIRTUS LAB 工作,在业界研究77GHz毫米波汽车雷达芯片,之后在复旦从事研究工作,硕士生导师。

主要研究方向为模拟射频集成电路:适用于5/6G毫米波通信的相控阵收发机芯片、锁相环PLL芯片、毫米波功率放大器芯片、77GHz FMCW 雷达芯片、高速有线通信芯片、新型MoS2芯片设计等。

集成电路通常采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在半导体衬底中。无论新型的二维芯片还是目前传统的硅工艺芯片,其芯片的设计的主要目的仍然是实现特定的功能。从集成电路器件到芯片的设计中间的桥梁就是定制的模型和特定的拓扑结构。

本次以目前两个热门的题目为例说明,首先新型的神经网络芯片。基于传统的硅工艺神经网络芯片需要大量的乘法和加法单元实现卷积的运算,如何实现低功耗高速的卷积运算是其中的核心问题,此外神经网络的输入通常为传感器的数据。传感器芯片和神经网络芯片之间通常需要接口,大量的数据通过接口传递会消耗大量的功耗和芯片的面积。实现传感和神经运算的结合是未来发展的重要方向,也是拟神经计算的关键。二维器件具有光、电、磁、气体等感应,基于二维器件实现传感是较为容易,但是基于二维的器件实现神经网络运算并不简单。相比于基于二维神经单元,通过软件实现神经网络而言,二维芯片实现神经网络并且集成前向传播网络芯片更具应用价值。如何实现?首先是器件的建模,器件的建模打破了传统二维芯片通过实验迭代的方式优化电路,而是通过仿真不断优化器件,从而实现快速高质量电路。

对于目前的5G和6G通信,毫米波芯片是传输的关键。对于毫米波电路而言,最为困难仍然是器件建模,随着频率的升高,传统的模型已经无法支撑高频电路的设计。因为电阻、电容和电感在超过100GHz以上的频率已经不仅仅是电阻、电容和电感,同时简单的一根线在低频的短路已经不在成立,需要通过传输线理论进行分析。同时晶体管的寄生电容已经不能忽略,需要通过准确的进行建模和仿真。因此如何设计毫米波芯片的核心在于建模和特定拓扑的优化。如何在硅的材料中通过实现不断的几何形状从而实现特定的电路功能是一个艺术。

⬛ 定制二维器件的spice模型与乘加运算

MoS2晶体管的建模是实现芯片的关键,MoS2晶体管SPICE模型的直流参数多达几十个,参数划分为三类,一类是器件本征物理参数,比如栅氧化层的相对介电常数和厚度,这些参数是由制备工艺确定的。第二类是器件的性能参数,在物理含义上有着明确的定义,比如阈值电压、输出阻抗等,是需要在测试结果当中提取的。第三类参数是经验性参数,这些参数在物理含义上并没有特定的定义,但是有的可以在物理现象中找到合理的解释,比如用来描述晶体管DIBL效应的参数AT和BT等,有的参数可能仅仅是为了曲线更加的光滑,更加的符合现实中测得的结果。

根据SPICE模型方程式和模型参数的分析,明确器件参数,在测试结果中提取物理参数,最后对于经验性参数,根据仿真结果和测试结果的对比,反复微调经验性参数,得到合理的值。在完整的得到MoS2晶体管SPICE模型的直流参数之后,进行仿真结果和测试结果的对比,如果符合预期,进一步对误差进行分析,并且通过单元电路的验证,来证明结果的可靠性。

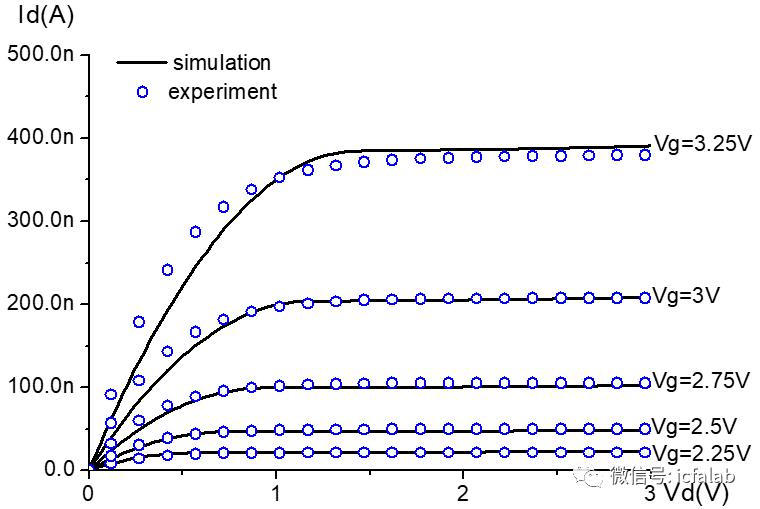

图1 晶体管(宽长比为90um/20um)的输出特性曲线

仿真与测试对比

仿真结果与实测结果吻合,误差主要出现在线性区,是由于肖特基接触导致的。在SPICE Level 62薄膜晶体管模型当中,对于肖特基接触的处理并不完善,是模型误差的主要原因。通过将仿真数据和实测数据进行比较,可以量化模型的误差。MAPE的计算方法是实测值与仿真值的差值的绝对值除以实测值,最后将所有的数据取平均值得到的,如下式,其中ai是实测值,bi是仿真值。

MAPE的平均值是4.56%。我们可以看到基本上误差都在5%以内,极少数的点的误差落在5%到10%之间,这表明模型结果非常准确。制备的反相器进行了SPICE模型的验证和分析。

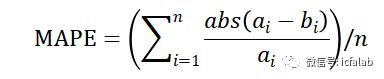

图2 基于MoS2晶体管搭建的反相器结构

示意图和测试图

如图2所示,是基于MoS2晶体管搭建的反相器仿真与实测对比图,虚线是实测曲线,实线是仿真曲线。该反相器可以正确的实现反相功能,翻转电压值约为0.27V,基本在0.2V范围内实现完全翻转,电压增益大于10。

⬛ 基于定制二维器件的神经网络芯片设计

图3 二维神经网络芯片【1】

制备了高质量均匀的两英寸二维MoS2晶圆,并开发了利于集成电路制造的增强型顶栅晶体管技术,在此基础上利用level-62 SPICE模型构建晶体管仿真模型,从而对人工神经网络中的模拟电路进行仿真和优化。如图3所示的二维神经网络芯片包括了多个神经元,每个神经元包括了信号输入、权重和信号的乘积(MAC)以及激活输出。MoS2增强型晶体管特性展示出了较大的电流开关比和良好的均一性,降低了大规模MoS2电路的集成难度。MAC单元中的乘法模块由一个定制的双栅晶体管组成,可以对输入信号和权重进行乘法运算。当多个该乘法结构的并行连接则可实现累加操作,其结果对应于总输出电流。因此采用多个Finger并联和双栅可实现MAC操作,从而将复杂的MAC操作在定制的MAC器件中完成,与需要大量晶体管的数字MAC电路相比,本工作中采用的模拟MoS2晶体管乘加网络在芯片面积、计算速度和功耗上都有着巨大优势。

⬛ 毫米波器件的模型设计与匹配设计

对于CMOS毫米波电路设计而言,晶体管模型的准确性以及各个参数的准确性都十分重要。工艺厂商提供的模型大多只在30 GHz以下的频率范围进行过测试验证,一个准确的晶体管模型在设计电路的时至关重要。

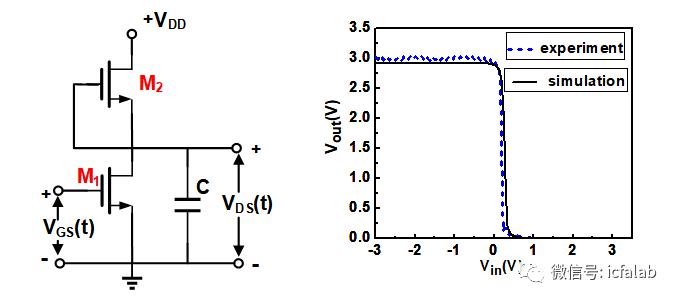

图4 CMOS晶体管小信号电路模型、版图与变压器版图

图4所示的是晶体管的小信号等效电路模型与差分版图,包含本征参数和寄生参数两部分,本征参数包括Cgs、Cgd、Ri、Rgd、Rds和Cds,外部寄生参数包括Lg、Rg、Ld、Rd、Ls和Rs。外部寄生参数主要是版图设计中的金属连线和过孔引入的。

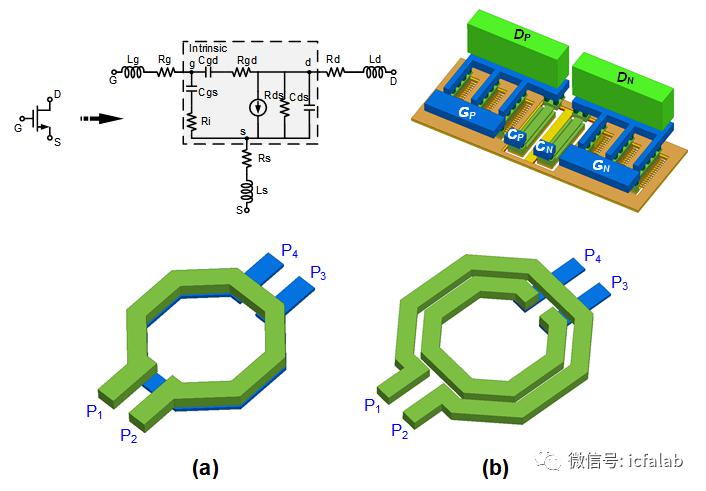

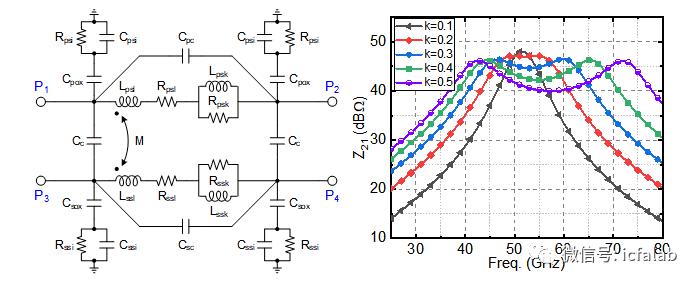

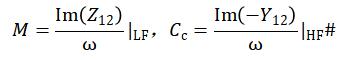

图5 集总参数模型与匹配后的Z21

变压器的为两个相互耦合的电感可以应用匹配设计如图5所示。图5展示了一个耦合的变压器集总参数模型,变压器模型中主级与次级线圈的模型参数均可以通过与单个电感模型相似的方法得到。在主级/次级线圈一端接地的条件下,变压器的耦合电容Cc以及互感M可以通过下式求得:

在片上非理想因素的作用下,变压器的主级与次级线圈在不同频率处将呈现出不同的电感,其电感值与对应的耦合系数可以采用下式计算。不同耦合系数k下的磁耦合谐振腔Z21仿真结果如图5所示。

⬛ 毫米波放大器设计

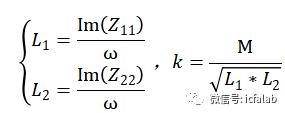

图6 140GHz功率放大器与版图【2】

基于晶体管模型和变压器模型,设计双路合成的功率放大器原理如图5所示。驱动级晶体管M1 & M2的尺寸为18 μm/30 nm,输出级晶体管M3的尺寸为18 μm/30 nm;其对应的中和电容尺寸分别为9.5 μm/30 nm与25 μm/30 nm。单路功率放大器的输入与输出阻抗均匹配至100 Ω,并且通过100 Ω特征阻抗的传输线进行功率分配/功率合成。图6显示出了该设计的各级宽带匹配网络所采用的低耦合系数变压器三维视图以及对应的匹配网络理想模型。该设计的四级匹配网络均仅采用单个变压器实现,具备极为紧凑的面积,芯片在135 GHz可以达到峰值增益21.9 dB,并且在128-147 GHz范围内增益均高于19 dB。此外,该功率放大器在120-150 GHz范围内均可以达到10 dBm以上的输出功率。

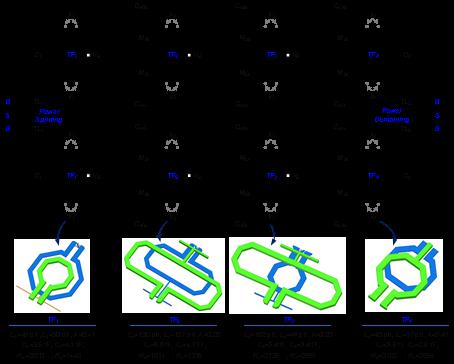

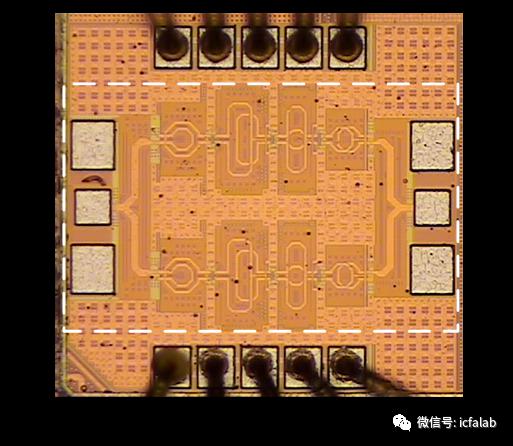

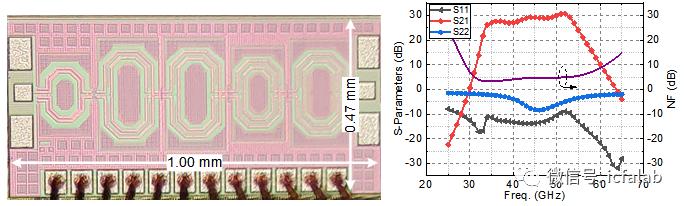

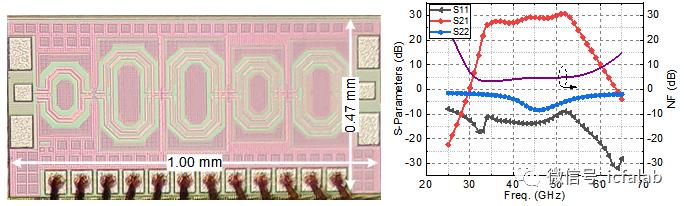

图7 5G毫米波低噪声放大器芯片【3】

低噪声放大器芯片的S参数测试结果如图7所示,最高增益为30.5 dB,3-dB带宽频率范围为35~50 GHz,1-dB带宽频率范围为38~48 GHz,在1.2-V电源电压下的直流功耗为63.6 mW。S11和S22参数测试结果和仿真结果也有较好的一致性,S11在30~65 GHz频率范围内都小于-10 dB。噪声系数采用噪声源346CK40和信号分析仪N9040B测试,在35~50 GHz频率范围内的噪声系数为4.1~6.5 dB。

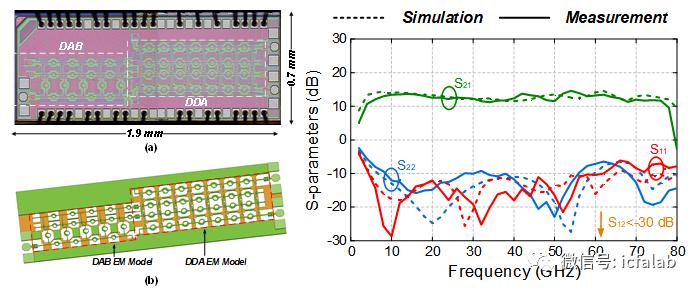

图8 CMOS分布式放大器芯片版图与测试

超宽带放大设计,该芯片的带宽可达75 GHz以上,而安捷伦N5247B矢量网络分析仪支持的最高频率为67 GHz,因此需要借助频率扩展模块将测量范围扩展至110 GHz。进行S参数测试之前需要进行校准以去除线缆、探针等器件的影响。图8展示了该芯片的S参数测试结果。该芯片的仿真与测试结果展现了非常好的一致性。该芯片的带内单路最大增益约为13.9 dB,且在3-78 GHz范围均大于11 dB;输入/输出反射系数在全频带内均低于-7 dB。

总结

集成电路器件到芯片的设计中间的桥梁就是定制的模型和特定的拓扑结构,只有对模型进行深刻的理解,对电路拓扑深入的分析,才能设计出优秀的电路,在二维材料与硅材料中雕刻出超越一般性能的电路,不仅仅是技术也是艺术。

来源:芯系清华

分享二维码到朋友圈免费为您发文章一篇

欢迎各公众号,媒体转载

投稿/推广/合作/入群/赞助/转发 请加微信13488683602