Q1

иҜ·ж•ҷдёӢпјҢAECQ-100еҒҡдәҶPTC,иҝҳиҰҒеҒҡTCеҗ—пјҹиҝҷдёӘжҳҜдәҢйҖүдёҖеҗ—пјҹ

A

йғҪеҒҡзҡ„пјҢPTCе’ҢTCдёҚдёҖж ·гҖӮ

Q2

иҜ·й—®дёӢеӨ§е®¶пјҢWLCSPзҡ„dieпјҢmarkingйқўеӣ дёәеңЁPCBиҫ№зјҳдҪҚзҪ®жңүcrackйЈҺйҷ©пјҢеҸҜд»Ҙз”ЁзӮ№иғ¶зҡ„ж–№жі•и§ЈеҶідёҚпјҹжҲ–иҖ…жңүеҫҲеҘҪж–№жі•дҝқжҠӨе‘ўпјҹ

A

з”ЁзӮ№иғ¶еҸҜд»Ҙж»Ўи¶ійҳІжӯўcrackзҡ„йЈҺйҷ©пјҢдҪҶжҳҜиҰҒиҖғйҮҸе…¶д»–йЈҺйҷ©пјҢжҜ”еҰӮж•Јзғӯй—®йўҳгҖӮжңүдәӣWLCSPжҳҜжңүеӨ–еҢ…еӣҙзҡ„пјҢеңЁPCBиҫ№зјҳпјҢWLCSPеӨ–дҫ§пјҢеҒҡдёҖдёӘй«ҳдәҺWLCSPиҠҜзүҮзҡ„йҮ‘еұһжҢЎзүҮпјҢйҳІж’һгҖӮ

Q3

е®ўжҲ·жҳҜз”ЁдәҶзұ»дјјCOBе°ҒиЈ…дёҖж ·зҡ„зӮ№иғ¶гҖӮдҪҶеӣ дёәзӮ№иғ¶д№ҹеҮәзҺ°дәҶdrop test д»ҘеҗҺзҡ„еә”еҠӣй—®йўҳпјҢbumpsжңүcrackпјҢжүҖд»ҘжғіиҜҙжңүжІЎеҗҲзҗҶзҡ„ж–№жі•йҳІжӯўи§Ұзў°пјҢжҲ–иҖ…дјҳеҢ–зӮ№иғ¶жқҗиҙЁпјҹ

A

еҠ underfillдјҡеҘҪдёҖдәӣпјҢSMTзҡ„ж—¶еҖҷеҠ underfillгҖӮ

Q4

A

bakingж—¶й—ҙе’Ңжё©еәҰжҳҜе’Ңwaferзҡ„processжңүе…ізҡ„пјҢдёҚжҳҜйҖҡз”Ёзҡ„пјҢдҪ иҰҒжҹҘдҪ зҡ„дә§е“Ғзҡ„processе·ҘиүәеҜ№еә”зҡ„specгҖӮ

Q5

иҜ·й—®дёӢOBIRCHжқЎд»¶и®ҫе®ҡгҖӮеӣ е…¶жҳҜдё»еҠЁејҸеҺҹзҗҶпјҢж•…жңәеҸ°иҰҒжҺҘдёҖи·Ҝз”өжәҗпјҢеҰӮдёҚжӯўдёҖз»„жқЎд»¶пјҢе…¶д»–еҮ и·Ҝз”өжәҗеҸҜдҪҝз”ЁеӨ–жҺҘз”өжәҗгҖӮжғіиҜ·ж•ҷдёӢпјҢеҪ“жңүеӨҡз»„жқЎд»¶ж—¶пјҢиҝҷеҮ з»„з”өжәҗиҜҘеҰӮдҪ•йҖүжӢ©пјҢе“Әи·ҜжҺҘе…ҘobirchжңәеҸ°пјҢе“ӘеҮ и·ҜеҸҜд»ҘеӨ–жҺҘз”өжәҗпјҹеҰӮжһңйҖүжӢ©й”ҷиҜҜпјҢеҜ№зғӯзӮ№жҲҗеғҸжңүж— е№Іжү°пјҹ

A

жҠҠжңҖзӣёе…ізҡ„з”өжәҗеј•и„ҡеҠ е…ҘеҲ°OBIRCHйҮҢпјҢ然еҗҺеӨ–зҪ®з”өжәҗжҺҘе…ҘеҒҸзҪ®е•ҠпјҢдҪҝиғҪзҡ„еј•и„ҡдёҠгҖӮ然еҗҺиҝҷдәӣз”өжәҗе…ұең°е°ұеҘҪдәҶгҖӮиҝҷдёӘжқЎд»¶иҰҒеӨҡе°қиҜ•жүҚеҸҜд»ҘпјҢжҜ•з«ҹе®һйӘҢеҮәзңҹзҹҘгҖӮдёҖж–№йқўжңүreference(еҘҪзүҮ) дҪңдёәеҜ№жҜ”пјҢеҸҰдёҖж–№йқўжӢҝеҲ°з–‘дјјзӮ№еҺ»жүҫз ”еҸ‘и®Ёи®әдёҖдёӢгҖӮ

Q6

иҜ·ж•ҷдёҖдёӢеҗ„дҪҚпјҢе®ўжҲ·е®ҡд№үйӘҢ收дә§е“Ғзҡ„иүҜзҺҮеңЁ100PPMпјҢжҳҜдёҚжҳҜеӨӘдёҘж јдәҶеҸҰеӨ–е…ідәҺе®ўжҲ·зҡ„е”®еҗҺй—®йўҳпјҢеҗ„иҙөеҸёдёҖиҲ¬жҖҺд№ҲеӨ„зҗҶгҖӮжҲ‘们д№ӢеүҚзҡ„е®ҡд№үжҳҜеҲ°е®ўжҲ·йӘҢ收д№ӢеҗҺпјҢйЈҺйҷ©иҪ¬з§»е°ұз»“жқҹдәҶгҖӮ

A

ppm иҝҷдёӘи·ЁеәҰ/еңЁдёҚеҗҢеә”з”ЁиҝҳжҳҜжҢәеӨ§зҡ„гҖӮ

жҜ”еҰӮ ST жҹҗsocиҠҜзүҮпјҢж¶Ҳиҙ№зә§е’Ңе·Ҙдёҡзә§з®—дёҖзұ»пјҢ50ppm

жҜ”еҰӮ Sierraй’ҲеҜ№жҷ®йҒҚе°ҸиҠҜзүҮпјҢж¶Ҳиҙ№зә§е’Ңе·Ҙдёҡзә§з®—дёҖзұ»пјҢ80~100ppm

жҜ”еҰӮQualcomm AP, з»ҷODMеӨ§жҰӮ500ppm

жҜ”еҰӮдёҡеҶ…жҷәиғҪеҚЎпјҢеӨ§жҰӮ2~3000ppm

е…¶е®һжңүж—¶дёҚжҳҜе®ўжҲ·иҰҒжұӮеӨҡе°‘пјҢе…¶е®һжҳҜиҮӘе·ұиғҪеҒҡеҲ°еӨҡе°‘пјҢиҮӘ家зҡ„иҠҜзүҮдёҖиҲ¬иҮӘе·ұеүҚжңҹеҒҡзҡ„з»Ҷзҡ„иҜқпјҢеҹәжң¬еҝғдёӯжңүж•°зҡ„пјҢmarginеӨҹдёҚеӨҹпјҢе…је®№жҖ§еҘҪдёҚеҘҪпјҢеҚЎзҡ„дёҘдёҚдёҘзӯүгҖӮ

Q7

A

иҰҶзӣ–е…ЁжҲ–иҖ…дёҚе…ЁпјҢеҝ…йЎ»еҠ дёҠеүҚжҸҗжқЎд»¶гҖӮжү«жҸҸеҶ…йғЁз®ЎеӯҗпјҢ ScanжңҖе…ЁгҖӮжЈҖжҹҘеҠҹиғҪжҖ§й—®йўҳпјҢSLTжңҖе…ЁгҖӮ

SLTе·ҘдҪңжЁЎејҸжҺҘиҝ‘EnduserдҪҝз”Ёж–№ејҸпјҢжүҖд»ҘжңҖе®№жҳ“жҠ“еҲ°й—®йўҳгҖӮ

Q8

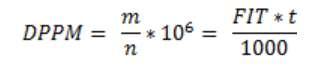

иҜ·ж•ҷдёӢеӨ§е®¶пјҢDPPMжҖҺд№Ҳз®—пјҹ

A

Q9

й—®дёҖдёӢеӨ§зҘһ们пјҢж–°зҡ„NANDж јејҸеҢ–дәҶдёҖ次然еҗҺжЈҖжөӢеҸ‘зҺ°дәҶ200дёӘеқҸеқ—пјҢд»Җд№ҲеҺҹеӣ йҖ жҲҗзҡ„е•ҠпјҢиҰҒжұӮжҳҜжңҖеӨҡдёҖдёӘгҖӮеҰӮжһңжҳҜеӣ дёәж јејҸеҢ–зҡ„ж—¶еҖҷз”өеҺӢдёҚзЁійҖ жҲҗзҡ„пјҢжҳҜдёҚжҳҜжҲ‘еҶҚж јејҸеҢ–дёҖж¬ЎпјҢеқҸеқ—ж•°йҮҸдјҡеҮҸе°‘гҖӮ

A

з”өжәҗеҺҹеӣ еҫҖеҫҖжҳҜеҫҲеӨҡй—®йўҳзҡ„дё»иҰҒеҺҹеӣ гҖӮж јејҸеҢ–зҡ„ж—¶еҖҷз”өжөҒеҸҜиғҪиҫғеӨ§пјҢеј•иө·з”өжәҗз”өеҺӢжіўеҠЁпјҢеҜјиҮҙйғЁеҲҶж јејҸеҢ–дёҚжҲҗеҠҹгҖӮеҲҶжһҗиҝҷдёӘй—®йўҳпјҢ1.з”ЁзӨәжіўеҷЁеҗҢж—¶йҮҸжөӢз”өжөҒе’Ңз”өеҺӢеҸҳеҢ–гҖӮ2.жҸҗдҫӣе№ІеҮҖзЁіе®ҡз”өжәҗеҲ°иҠҜзүҮпјҢзңӢзңӢжҳҜеҗҰз»“жһңжңүеҸҳеҢ–пјҢжқҘеҲӨж–ӯжҳҜеҗҰжҳҜеӣ дёәз”өжәҗй—®йўҳгҖӮ

еҰӮжһңз”өжәҗй—®йўҳе·Із»ҸжҺ’йҷӨжҺүпјҢ第дәҢдёӘеҸҜд»ҘжҖҖз–‘жҳҜtimingй—®йўҳпјҢж—¶й’ҹиҙЁйҮҸпјҢж—¶й’ҹйў‘зҺҮпјҢдҝЎеҸ·зҡ„setup timeпјҢhold timeпјҢдёІз»•пјҢеҸҚе°„зӯүзӯүгҖӮ

жқҘжәҗпјҡдёҠжө·еӯЈдё°з”өеӯҗ

ж¬ўиҝҺеҗ„е…¬дј—еҸ·пјҢеӘ’дҪ“иҪ¬иҪҪ

жҠ•зЁҝ/жҺЁе№ҝ/еҗҲдҪң/е…ҘзҫӨ/иөһеҠ©/иҪ¬еҸ‘ иҜ·еҠ еҫ®дҝЎ13488683602