由于提供支持图案后关键尺寸变化和掩膜重叠公差的工艺窗口的要求,高级节点的互连和通孔光刻的进一步缩放受到了挑战。

最近,在旧金山举行的国际电子器件会议(IEDM)上,台积电展示了其工艺开发活动的研究进展,已实现3nm节点的“自动对准通孔”(SAV),互连+通孔流程可以提高其制造性。本文总结了他们演讲的亮点。

01

介绍

过孔的可制造性需要解决多种光刻、电气和可靠性措施:

- 对叠加变化的容忍度(又叫做“边缘放置错误”,或EPE)

- 通孔电阻的一致性

- 通孔到相邻金属介电特性的稳健性

- 漏电流

1.击穿前的最大外加电压(Vbd)

2.介电可靠性,测量为随时间变化的介电击穿(TDDB)

来源:IEEE

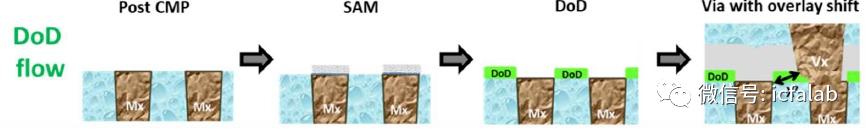

来源:IEEE- 自组装单层(SAM)沉积在金属上

- 选择性介电对介电(DoD)沉积

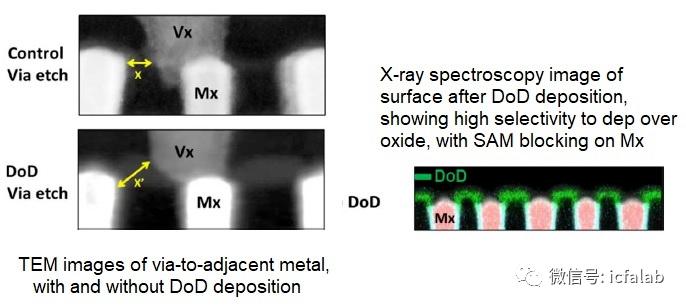

SAM阻挡层阻止了在暴露的电介质上的选择性沉积。如前所述,阻挡层必须经受住电介质上电介质选择性沉积的高温。台积电表示,更高的DoD工艺问题提高了电介质基座对周围用于通孔的低K层间电介质的刻蚀选择性,这将在接下来讨论。 上图中标记为“DoD”的图像说明了在电介质上电介质沉积之后以及在添加低 K 电介质之前去除晶片上的 SAM 阻挡材料之后的晶片。 上图也表现了在低 K 电介质沉积/蚀刻和通孔图案化之后的最终通孔连接。由于与低 K 材料相比蚀刻速率较低,因此添加了 DoD 材料服务器作为合适的“蚀刻停止”。该图像说明了存在显着覆盖偏移的通孔到相邻金属电介质。 下图说明了增加的电介质上电介质层如何提高通孔鲁棒性。“对照”透射电子显微镜图像(没有 DoD)显示原始电介质的过孔蚀刻过多,与相邻的 Mx 线几乎没有隔离——不是特别容忍重叠错误。DoD TEM 图像显示隔离度大大提高。

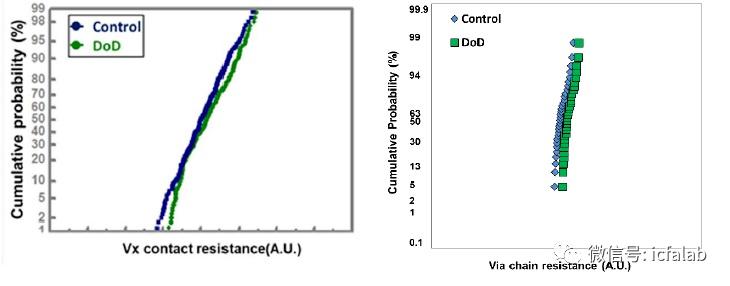

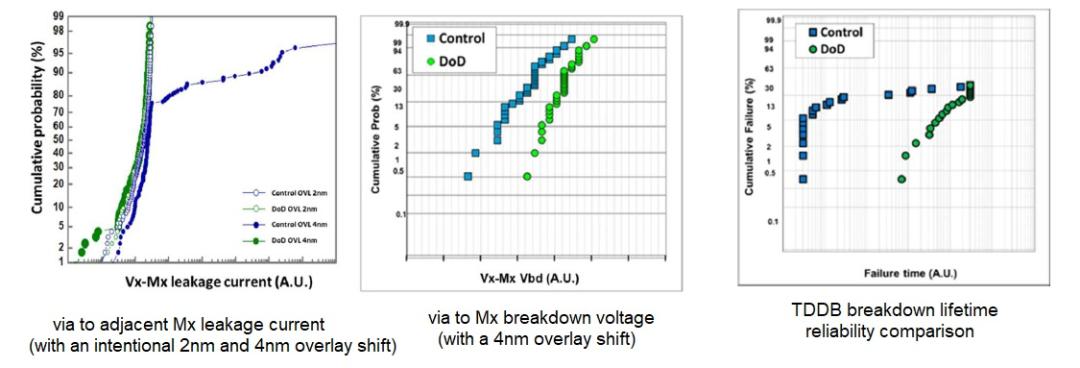

03SAV 过程的实验电气和可靠性数据 下面的各种图显示了来自台积电 SAV 工艺开发团队的实验数据。控制数据反映了没有选择性 DoD 层沉积的通孔图案化工艺的标准。

- 通过电阻

- 过孔到相邻的 Mx 可靠性(漏电流、Vbd、TDDB)

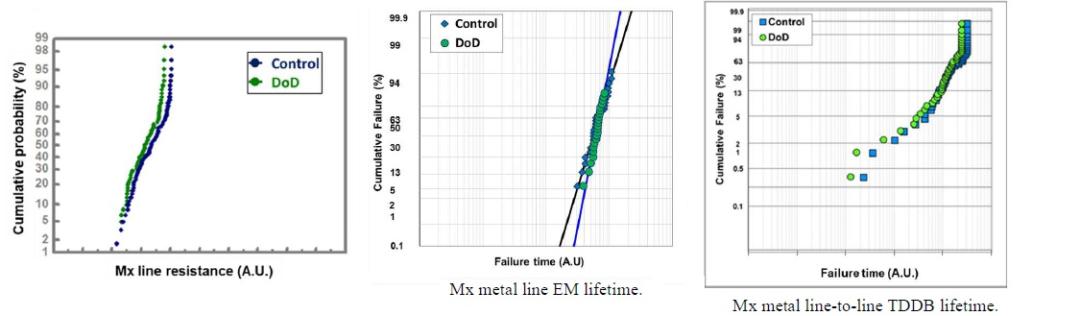

为确保额外的 DoD 工艺步骤不会对现有 Mx 金属的特性产生不利影响,台积电共享了有和没有 DoD 工艺的金属线的评估数据。下图显示对金属线电阻或 TDDB/电迁移可靠性没有影响。

3nm 节点以下的持续互连缩放将需要独特的工艺开发研究,以在存在(高达 4nm)重叠错误的情况下保持电气和可靠性规范。对低K层间电介质的需求是给定的——然而,这些材料中的通孔蚀刻并不是特别耐受EPE。 台积电已经展示了一种潜在的“自对准通孔”工艺流程,其中包含额外的 DoD 材料。DoD 的蚀刻速率差异导致了更强大的通孔到相邻金属的可靠性。该工艺流程采用两个独特的步骤——金属表面阻挡材料的 SAM 和电介质上电介质的选择性 ALD。 希望选择性 ALD 流程将很快从研发过渡到生产制造——这种化学物质对先进节点缩放的潜在影响是巨大的。

来源:旺材芯片

赵工

zhaojh@kw.beijing.gov.cn

欢迎各公众号,媒体转载,申请加白名单秒通过

投稿/推广/合作/入群/赞助/转发 请加微信13488683602