原创 CEIA电子智造 CEIA电子智造 2021-12-16 19:00

本期带来SiP技术专家李扬老师在CEIA电子智造北京站现场讲授的精彩课程。李扬老师作为IEEE高级会员,在半导体封装领域拥有20余年工作经验,曾参与和指导各类SiP项目40多项,在封装设计方面有自己独到的思考和见解,希望大家在阅读本文后有所收获,欢迎在评论区留言。

CEIA电子智造的朋友们大家好,我是李扬,今天我要分享的题目是先进封装与异构集成。

什么是先进封装?我们先来看一下先进封装的定义和特点,先进封装这个词现在非常热门,它的英文称为Advanced Package,有时候也被称为高密度先进封装HDAP,是当前封装技术发展的热点,从晶圆厂到封装用户再到系统用户,整个半导体业界都很关注。先进封装的定义,我这里用了一句话来概括,就是采用了先进的设计思路和先进的集成工艺,对芯片进行封装级的重构,并且能有效提高系统功能密度的封装,我们称之为先进封装。

大家会问,什么样的封装是先进封装?目前来说业界普遍认为大概分为这四类,比如说倒装焊、晶圆级封装、2.5D封装以及3D封装,图中我用了另外一种颜色来标注倒装焊,因为大家都知道,实际上倒装焊相对来说已经不是很先进了,这里我们可以感受出来,先进封装是一个相对的概念,并不是说某项技术是一直先进的,所以我们更关注的可能是下面这三个:晶圆级封装、2.5D封装和3D封装。

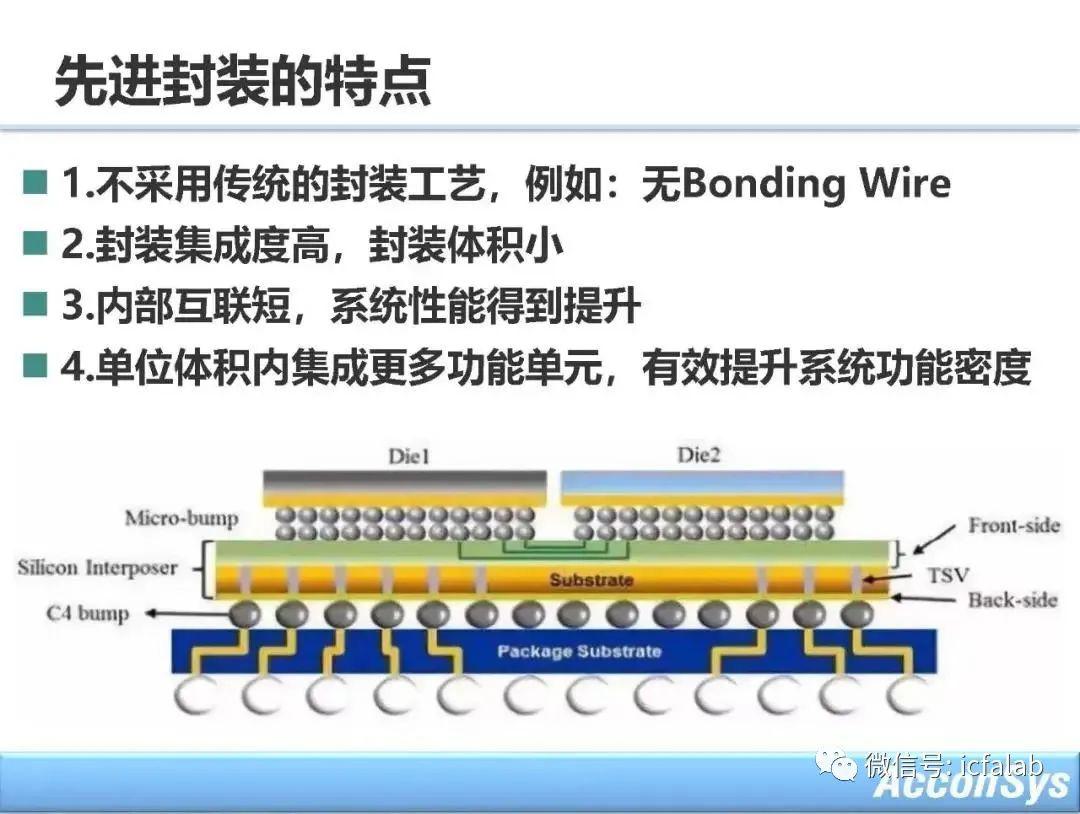

先进方案有什么特点?首先,先进封装不采用传统的封装工艺,比如说一般情况下先进封装不会采用传统封装里最常用的键和线(Bonding Wire),所以先进封装的集成度非常地高、封装体积很小,另外先进封装里面的互连非常短,系统性能会提高很多,大家看到现在有些像AMD或者像英特尔提出的一些先进封装可以使产品性能显著提高,另外就是先进封装里面能够集成更多的功能单元,能有效提高系统的功能密度,上面这个图就是比较典型的先进封装。

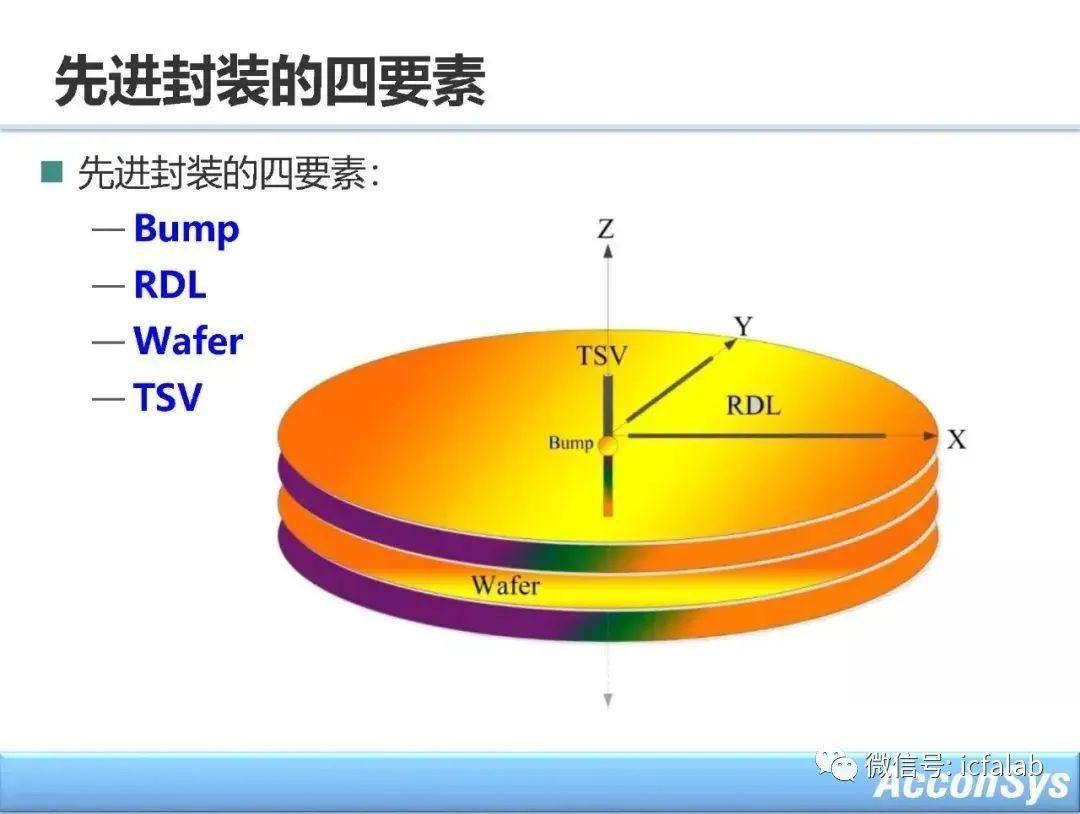

这个是我对先进封装四要素的总结,怎么判断是否为先进封装?我们从这几个点去判断,首先有没有Bump(凸点)?有没有RDL(重新布线),是不是采用了Wafer(晶圆层)?有没有TSV(硅通孔技术),这四要素中只要具备其中的一个或者两个,我们就定义它为先进封装。

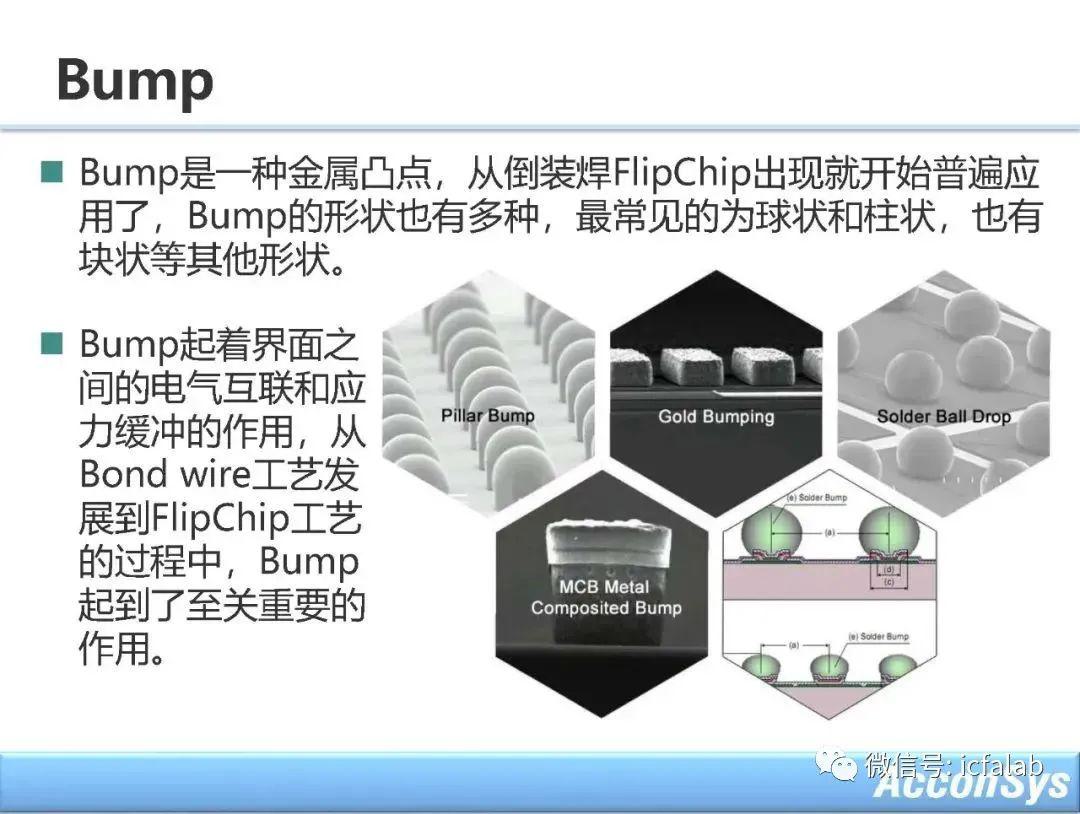

首先我们来看Bump,倒装焊里面用到的就是Bump,包括BGA、球这种,都是类似Bump,是一种凸点,有各种各样的形状。上图里有很多这种形状,它主要是起到界面的互连以及应力的缓冲等作用。从Bond Wire发展到Flip Chip工艺,Bump非常重要。

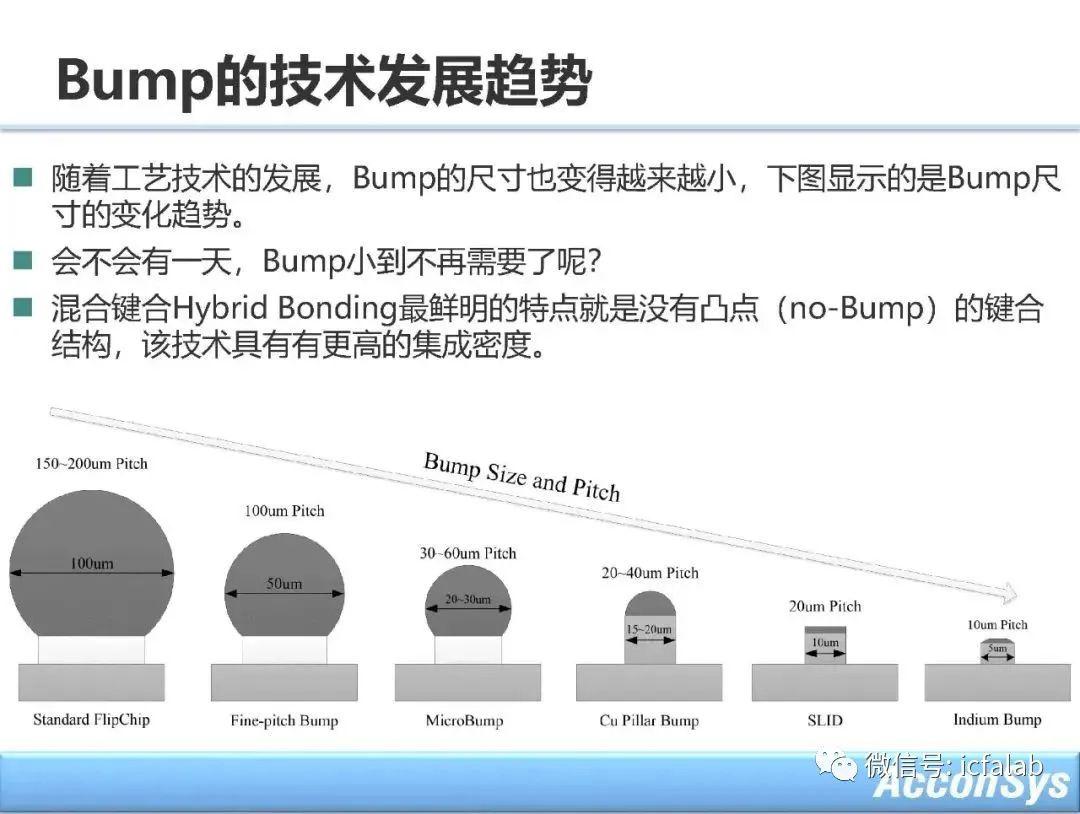

大家看,Bump的发展过程是在不断地变小,如上图,从100微米一直到现在的铟Bump缩小为5个微米,在这张图里,我提出来一个疑问,这个Bump会不会越来越小,最后就不再需要了?确实是这样的,目前,密度最高的叫Hybrid Bonding(混合键合),英特尔和台积电都在这上面发力,它的特点就是没有Bump,芯片和芯片直接就键合了,所以它的集成度非常地高,Bump随着以后的技术发展,很有可能是会消失的。

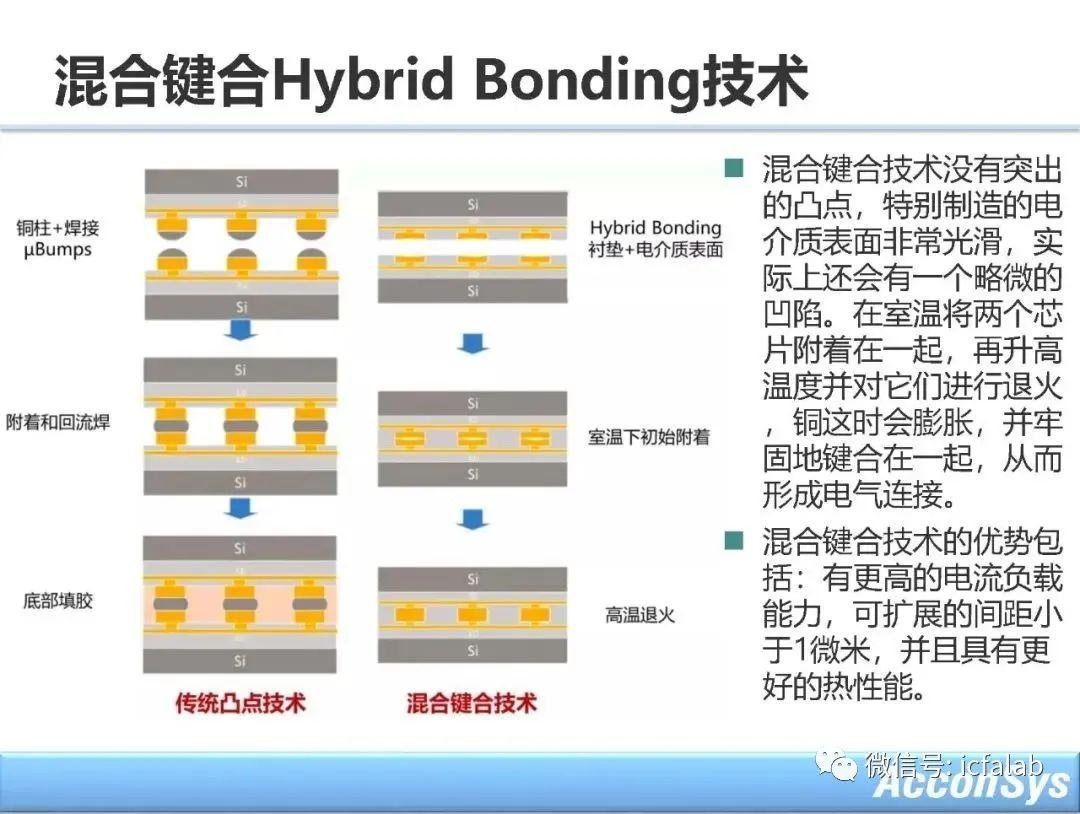

这里大家看一看混合键合技术和Bump技术的比较,混合键合没有这种凸起,直接就在室温下附着,然后高温就连在一起。它的特点就是因为中间没有底部填胶,所以散热性能更好,电气性能也会更好,可扩展间距小于一微米,密度非常大,混合键合技术将是Bump技术未来发展的方向。

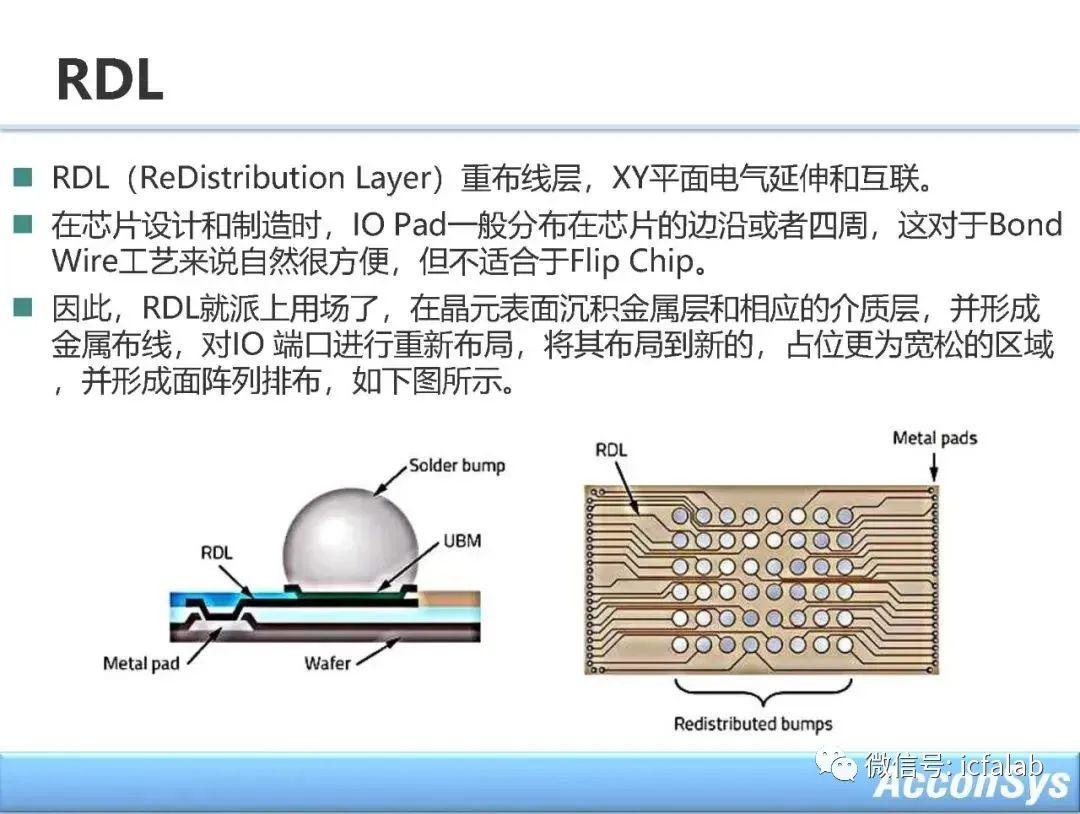

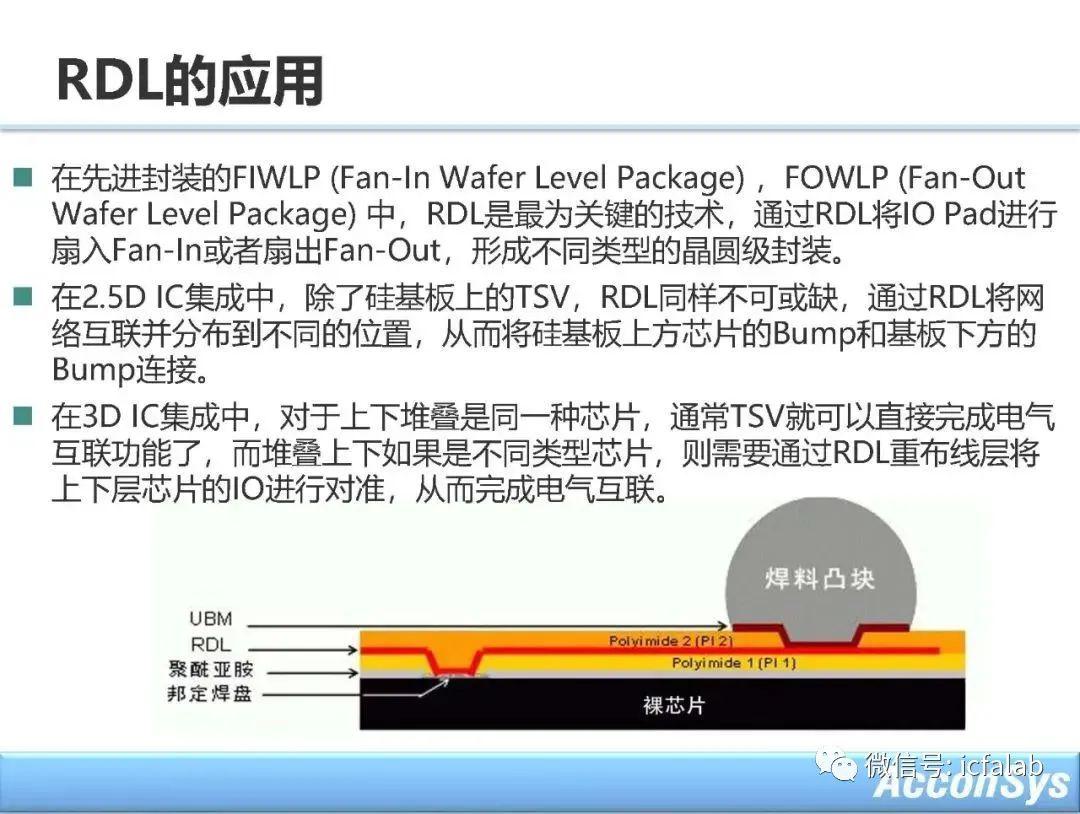

RDL是什么?RDL很像我们PCB上的布线,叫重新分布层,芯片做键合线的时候,键合线引脚都在外面一圈,有些时候我要做倒装焊的时候,就要把这个引脚做一下重新分布的位置,这时候就需要布一些线,然后这些层被称为重布线层,就是从边上那些引脚引到中间,这就是RDL。

RDL有两种类型,一种是往里面扇,叫扇入型(Fan-In),另外一种往外扇,叫扇出型(Fan-Out)。

扇出型和扇入型的区别就是往芯片中心走的那个叫扇入,往外部的话没有空间了就会做一个Molding把这个Bump扇出到外面去,在2.5D IC里面,就是硅基板那一类里面,也是有RDL的,RDL实际上我们的理解就是在XY平面上的一种延伸。RDL的应用是非常普遍的,除了在芯片表面和在硅基板上,还有就是在3D IC对准的时候也都会用到。

关于Wafer晶圆级封装,说到半导体封装,以前我们的理解就是把晶圆给切成粒,把每个芯片切开,然后给包裹起来、封起来。和传统半导体封装相比,晶圆级封装存在显著差异,它不像传统的封装那样先切割再封装,而是先在晶圆上封装完以后再切割,这就是晶圆级封装,因为整个工艺都是在晶圆上做的。

晶圆有三种作用,一种是作为芯片制造的基底,第二种是可以作为2.5D封装中所用到的硅中介板,还有一种作用就是作为晶圆级封装的载体。

正如我刚才讲的,Bump越变越小,最后小到没有了,但晶圆与之相反,正在变得越来越大,现在比较主流的大规模集成电路的晶圆是12英寸,就是300毫米晶圆,下一步的话会发展到450毫米,也就是18英寸的晶圆。当然现在6英寸的和8英寸的晶圆还在应用于一些小的芯片上,模拟电路啦、射频也还是会用小的晶圆,但是大规模集成电路的趋势就是会越来越大,只要工艺允许,晶圆尺寸大了以后效率提高,成本也会降低。

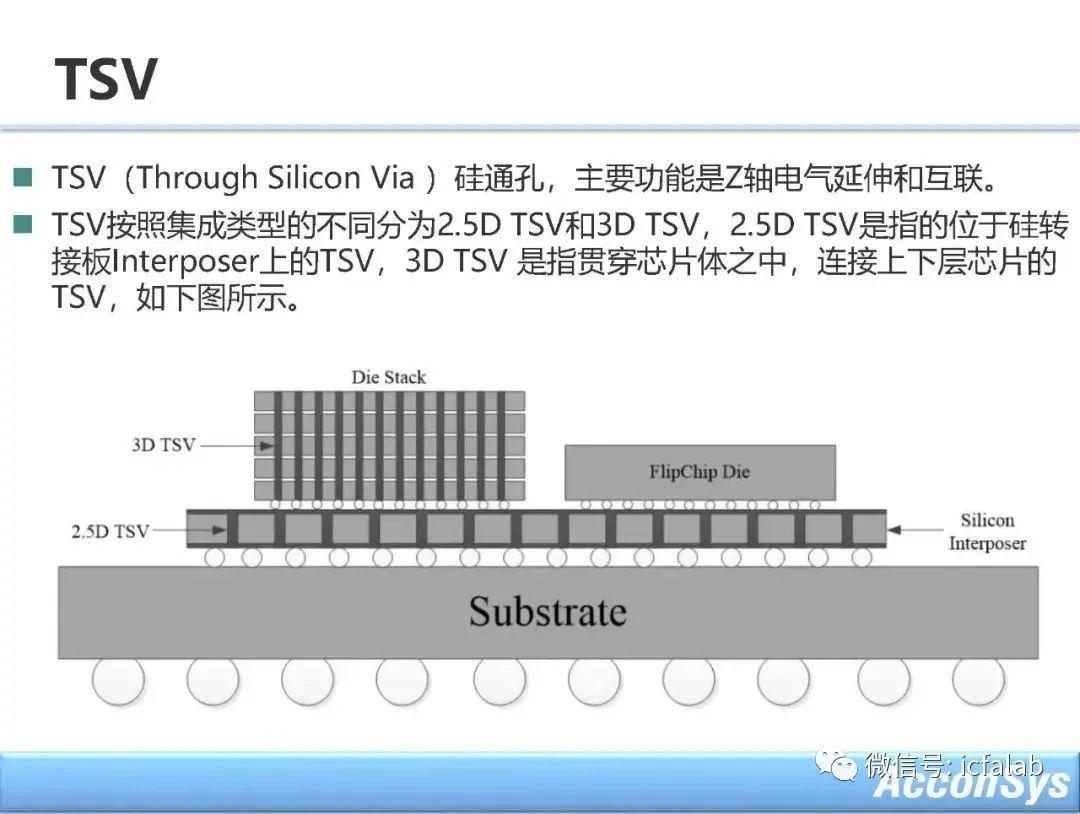

TSV叫硅通孔,主要的功能是实现Z轴的电气延伸和互连,为什么先进封装这么火,就是因为它能在Z轴上进行延伸,最主要的媒介就是TSV,把芯片打穿了,上下间电气连接起来了,由TSV把硅基板上下连接起来,这样的话电气就会互连得非常短,所以TSV这个技术现在研究得是最多的。

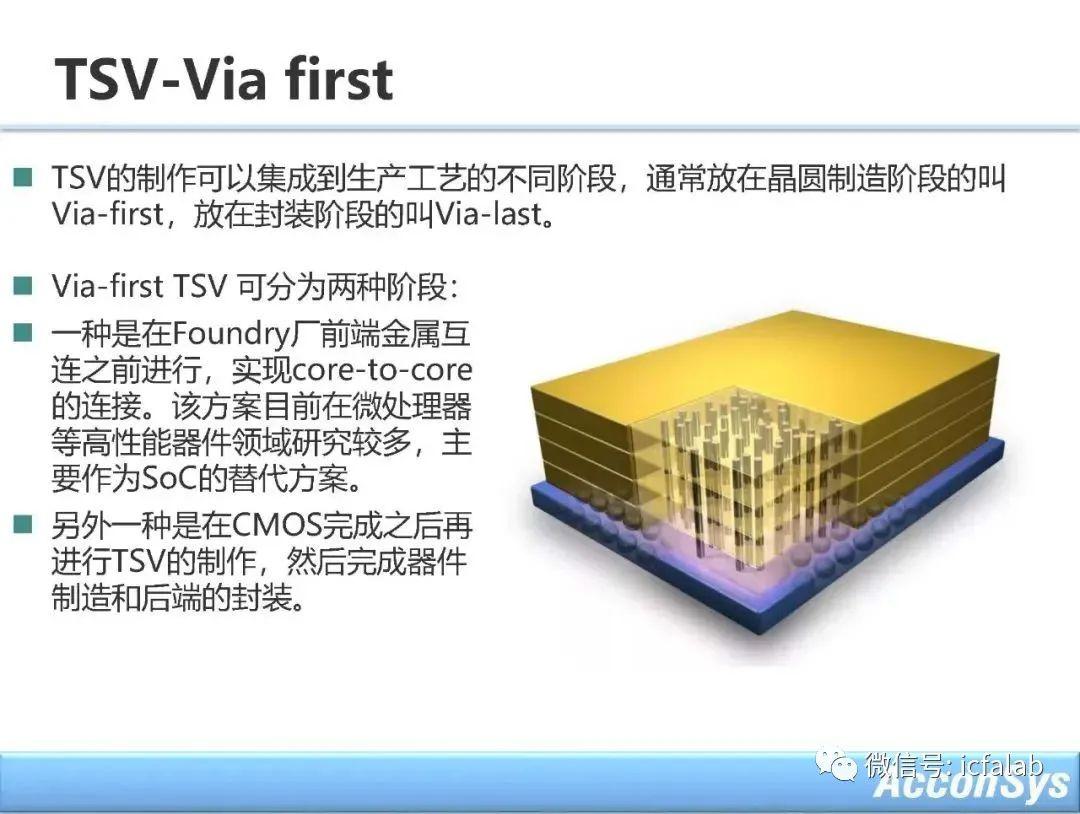

TSV有很多种,有一种叫TSV-Via first主要是在晶圆厂里做的,比如说在台积电、在中芯国际,它们的TSV就叫TSV-Via first,又分为两个阶段,一种是在金属互连之前进行,一种是在互连之后进行的,具体咱们今天不讨论,反正知道它们都是在晶圆厂里完成的。

另外一种是TSV-Via last,就是我们在封装的时候,一些封装厂比如说像日月光、安靠,它们在做的时候叫TSV-Via last,是在后端的,TSV-Via last一般就是说在芯片的周围打孔,芯片上不是说所有的地方都可以打孔,不能把芯片体打坏,只能在有空余的地方。TSV-Via last尺寸会比较大一些,TSV大家看到从1微米到100微米都有可能,所以范围变化很大。

目前的话,在一平方毫米的硅片上可以制作的TSV数量可以达到10万到100万,密度非常地大,但是大家也知道工艺上发展是有极限的,工艺的发展大家知道目前在一平方毫米的硅片上可以加工的晶体管数量已经超过1亿个,TSV的话可以做到10万到100万,所以密度都非常大,跟板级相比而言,属于微观级别。这种基本上就是用微米来描述,在芯片内部的话则基本上是纳米级。

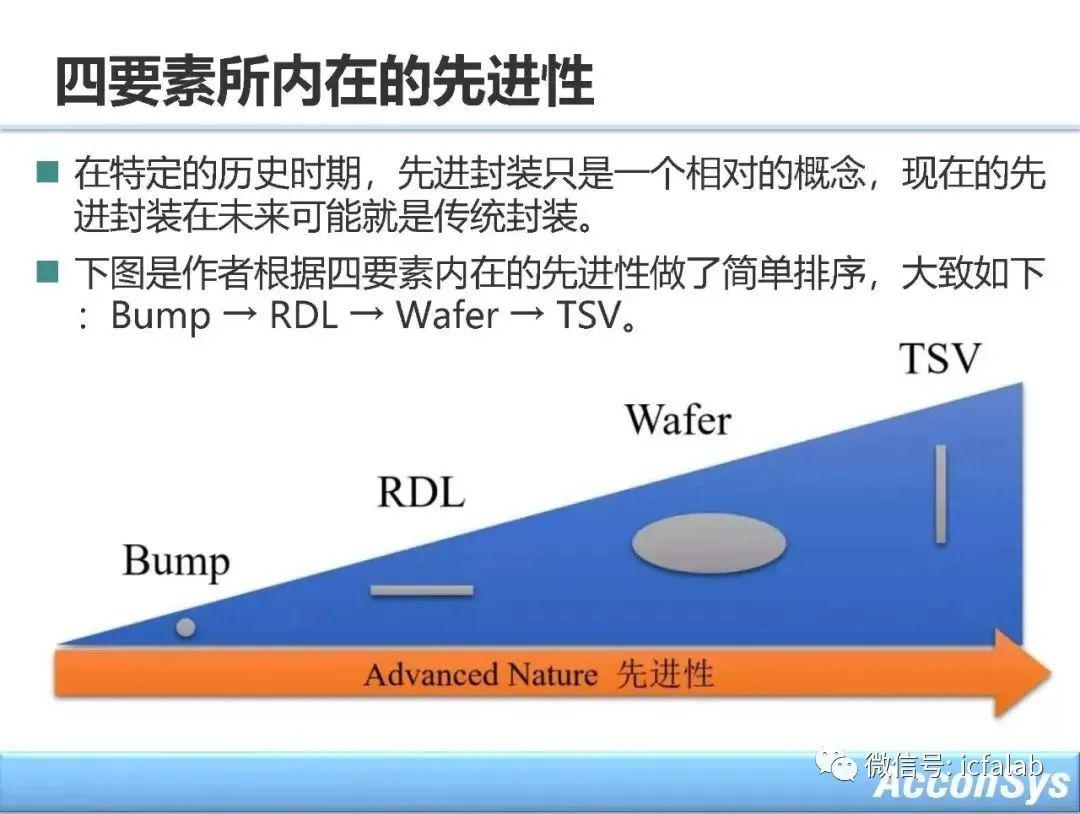

这里做一个小结,关于这四个要素,哪种要素代表的先进性更强,我认为它存在一个递进关系,就说从Bump到RDL到Wafer到TSV,越往右,实际上代表的先进性就越高,这当然不一定是百分之百准确的,但这是我的一种理解,这样列出来也方便我们大家记忆。

还有许多工程师跟我讨论的时候,有时会混淆先进封装和SiP系统级封装的概念。这两个概念是同一个东西吗?有人认为它们是一样的,也有人认为它们不一样,为了清晰地区分这两个概念,我特地画了一张图,列举了一些异同点的对比。

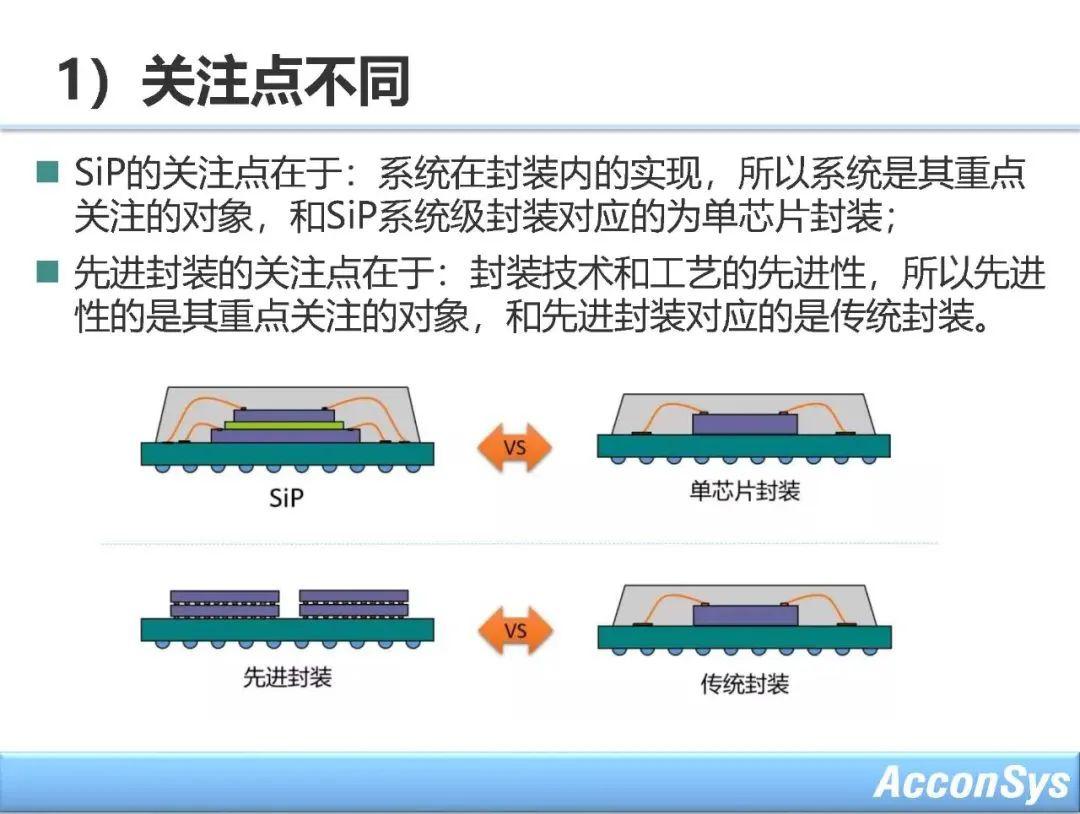

首先是关注点不同,SiP关注的是系统在封装体内部的实现,以前如果人们想要实现一个系统的功能,需要在一块PCB板上组装元件来实现,而现在将系统的功能浓缩到封装体的内部,所以和SiP相对应的是单芯片封装,因为SiP通常是多芯片的,要形成系统,你不可能是一块芯片。

先进封装的话,不管是多芯片还是单芯片,它更多的是关注工艺的先进性,是不是采用了RDL或TSV这些技术,所以与先进封装相对应的是传统封装,先进封装里一般不会采用键合线(Bonding wire)这样的工艺,上图可以看出来,与SiP相对应的是单芯片封装,与先进封装相对应的是传统封装。

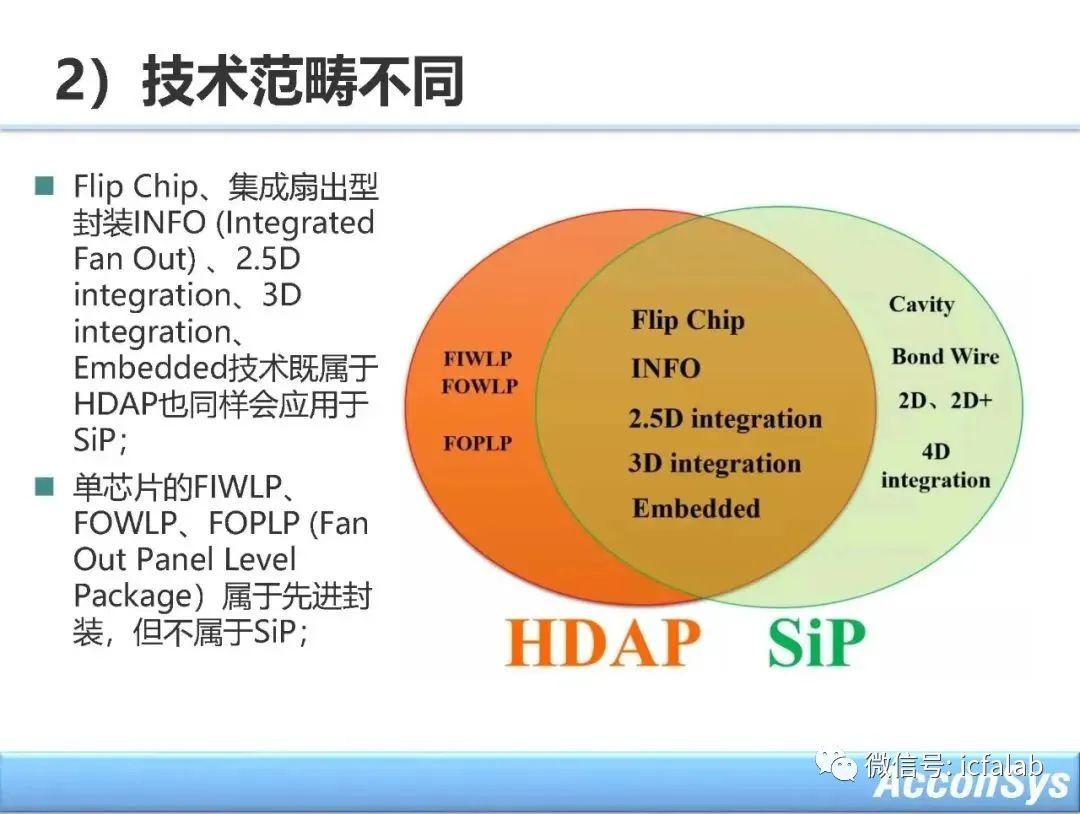

先进封装和SiP之间的另一个区别是它们的技术范畴不一样,先进封装是橙色这一块,实际上包含了Fan-in的Wafer level package还有Fan-out wafer level package,还有Panel level package,这些封装通常是单芯片的,而SiP的话还包含腔体封装、引线键合、2D、2D Plus、4D集成等封装。中间这部分是它们两者共同包含的,比如说Flip chip、INFO、2.5D集成和3D集成,这些它们都可以去含有。

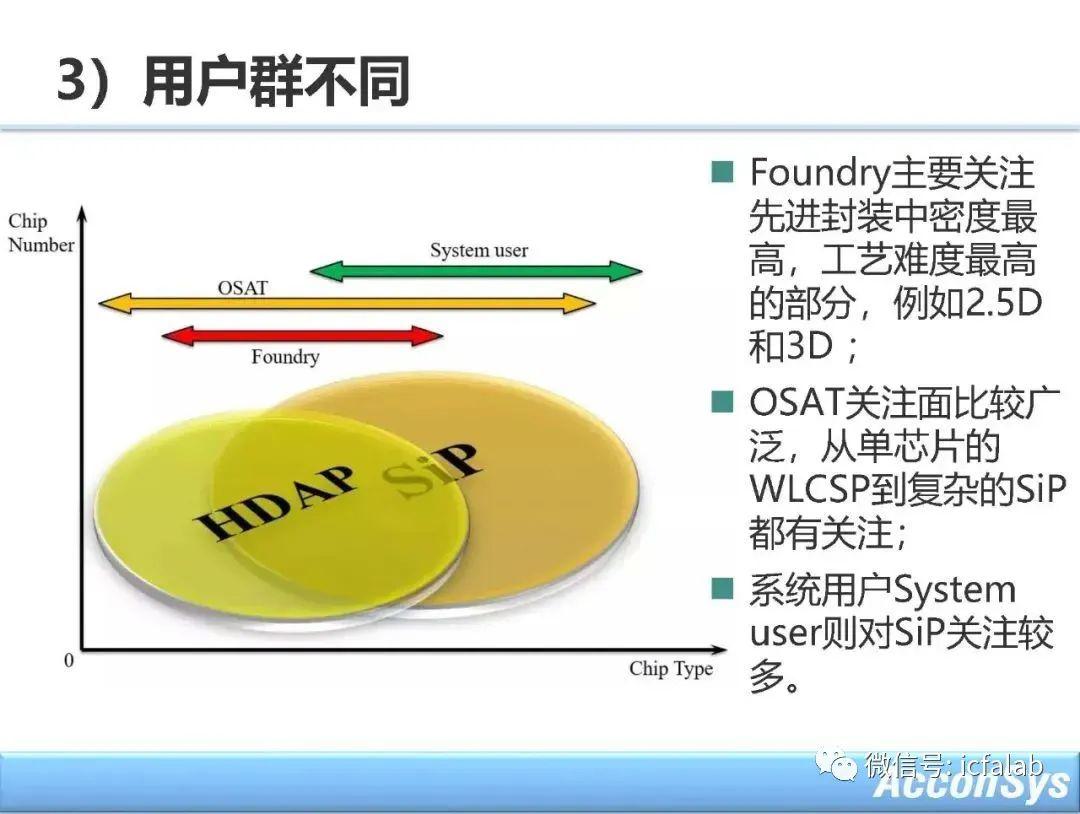

最后一个是用户群体不同,总体而言,Foundry(芯片代工厂)主要关注的是先进封装工艺,比如说台积电、英特尔、SMIC(中芯国际),它们关注的更多是2.5D、3D的先进封装工艺。而OSAT,我们常说的封测厂,关注的技术则比较全面,它们关注SiP、也关注Wafer level package,像苹果、华为这样的系统用户、以PCB作为产品载体的用户,更关注SiP的发展。

先进封装和SiP的特点,它们所具备的优点就是能够满足小型化、低功耗、高性能的应用,能够解决目前电子系统集成的瓶颈,CEIA电子智造的平台上曾经分享过许多关于板级集成的案例,大家会发现,如果封装技术存在限制,封装体的体积就比较大,这样产品中元器件的密度也就上不去,但如果能在封装体里面做一次集成,密度就比较高了,但是它需要裸芯片。目前在裸芯片的供应链以及芯片间的接口标准方面还需要提升和改善,比如说现在封装好的芯片很多地方可以买到,但是要买晶圆就没那么容易了。

另外一个比较热门的概念叫Chiplet(小芯片),还有一个叫异构集成(将分开制造的不同元件集成到更高级别的组件中,可以增强功能并改进工作特性),对于这些概念大家都给出了积极的反响,这代表着以后的趋势就是慢慢也会以提供的晶圆作为一种标准,我提供Chiplet,Chiplet就是小芯粒,然后再加上异构集成这个概念,也许10年以后大家去买芯片的时候,可能买的都是没有封装的,我在封装内去集成,这就是以后先进封装、SiP发展的一个趋势。所以SiP和先进封装有一定的重合性,但是不完全等同,有各自的特点。

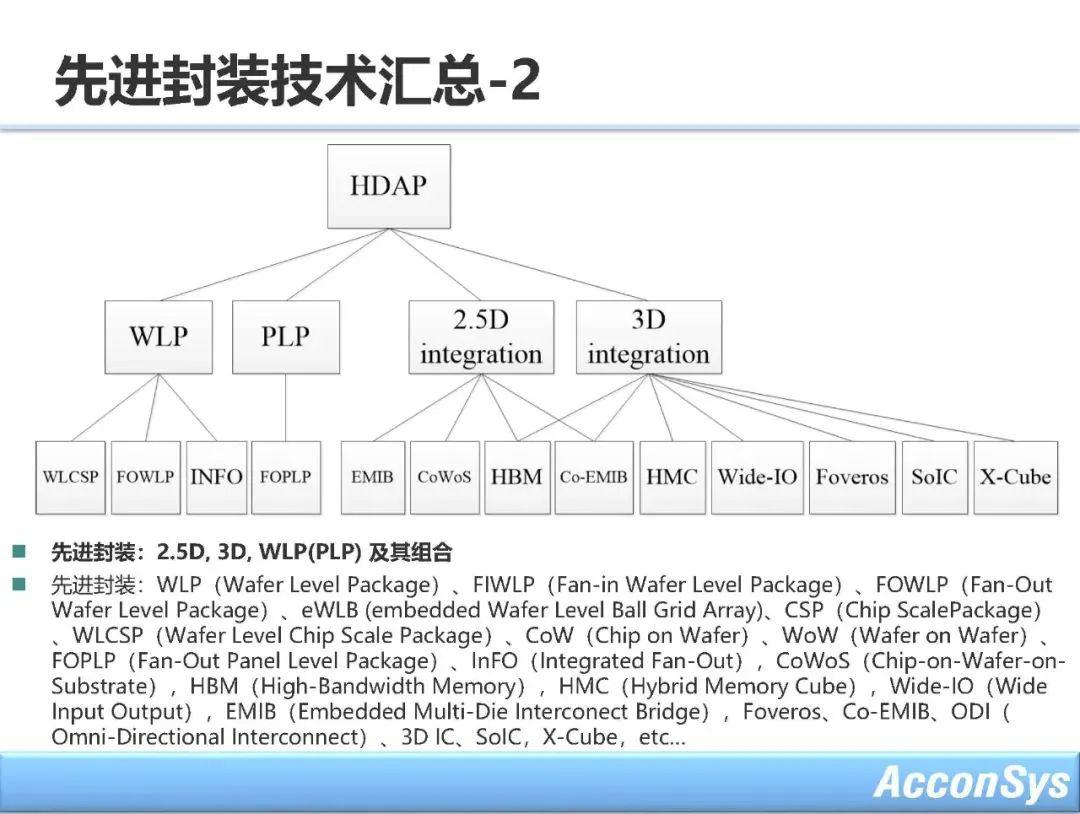

先进封装的技术特别多,有几十种。为了做了区分,我把基于XY平面延伸的先进封装技术和基于Z轴延伸的先进封装技术进行了分类。

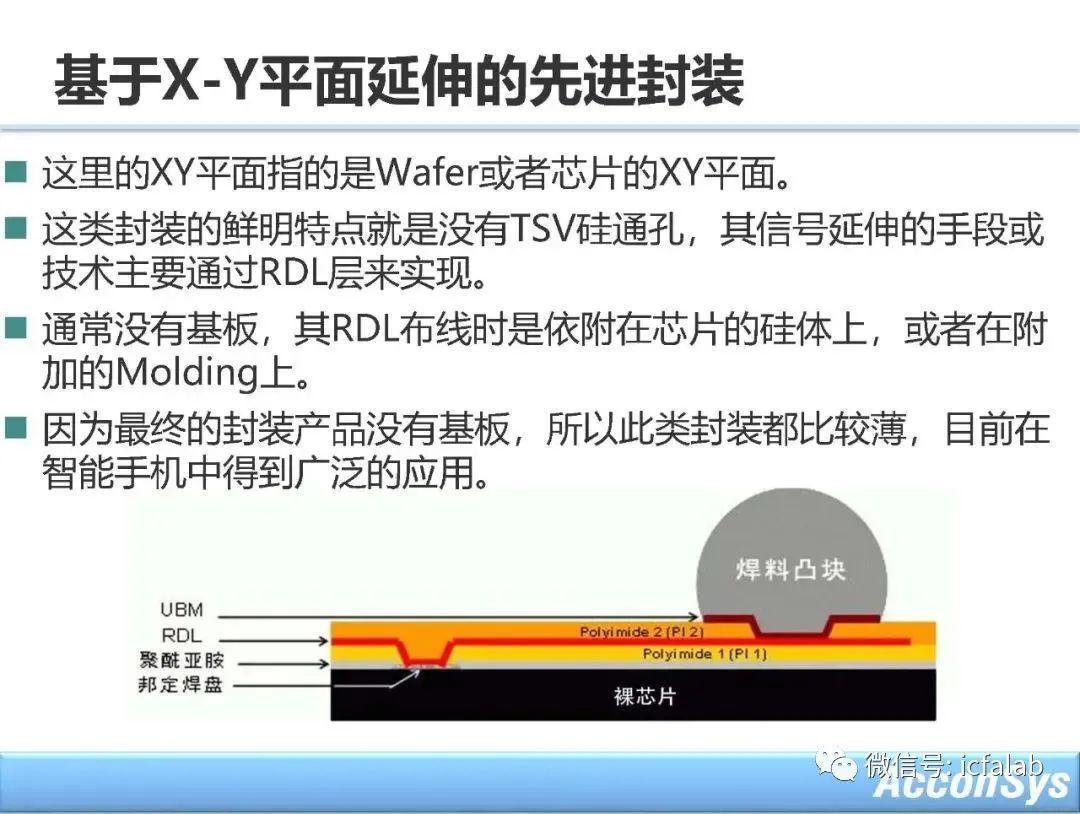

基于XY平面延伸的先进封装,主要指的是在Wafer的平面上或者是芯片的平面上,这一类封装没有硅通孔,它的延伸手段主要是通过RDL来实现的,通常没有基板。RDL依附在芯片的硅体上,或者在附加的Molding上,这类封装都比较薄,目前在手机上用得非常多。大家都知道,以前苹果的手机很多都由三星来代工,后来台积电就把大单抢过来,苹果好像是有一个型号,全部都是在台积电做的,因为采用了这种技术,芯片做得很薄,性能也非常好,成本还低。

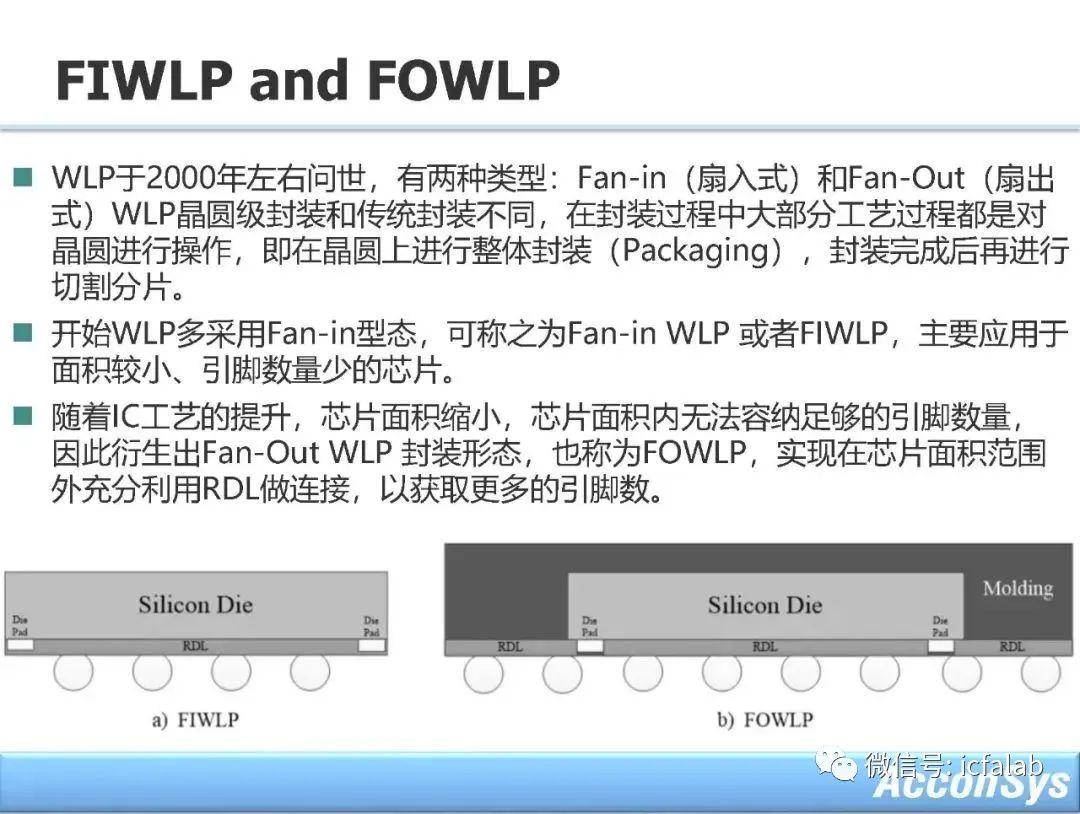

我们看看Fan-in wafer level package和Fan-out wafer level package,左边的叫Fan-in,右边的叫Fan-out。Fan-in就是说芯片的引脚都在边上,然后要把引脚引到中间去,往中间走,Fan-in就是往里面扇,另外就是Fan-out,因为往里面扇的时候空间有限,放不下怎么办?就给外面先做一层Molding,把它弄大,然后里外都可以扇,这种就叫Fan-out,实际Fan-out里也有往里扇的部分,Fan-out可以尺寸更大,它可以容纳的引脚数更多。

目前来说,比较热门的是Fan-out的工艺,因为像Fan-in的话,以前倒装焊都是Fan-in的,现在往外的引脚数更多。

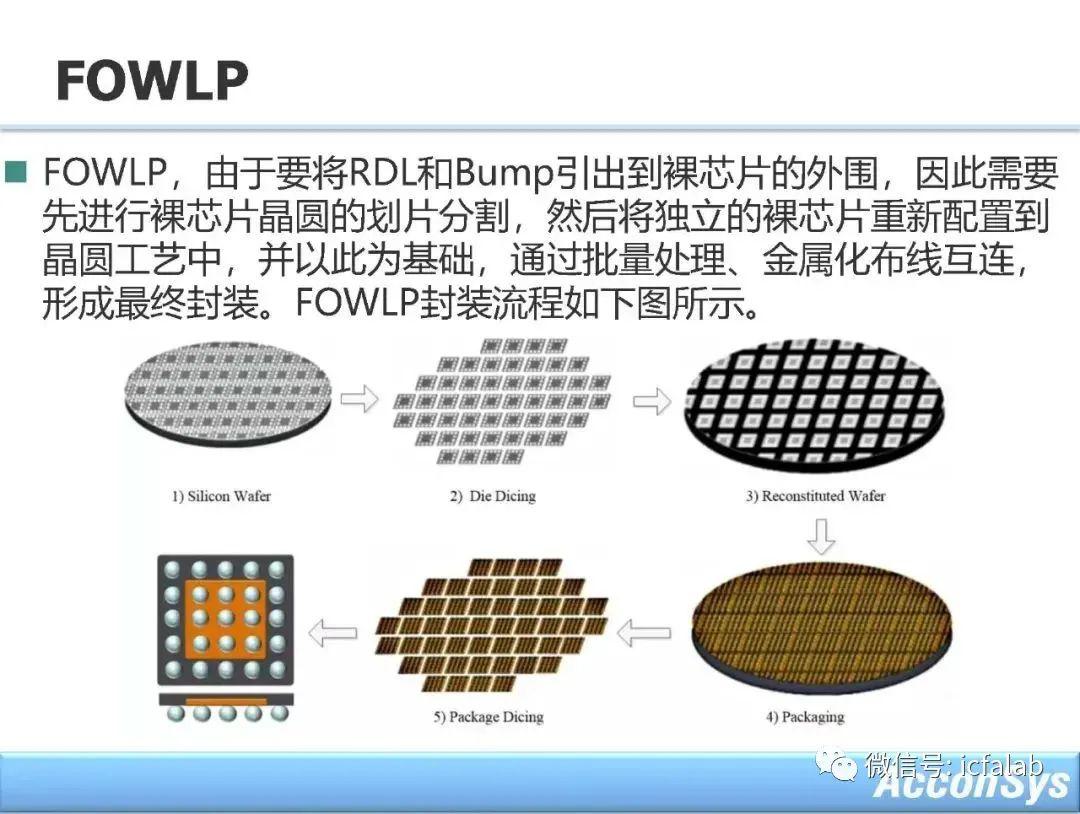

上图中展示的就是Fan-out Wafer level package这种技术,我们看,首先晶圆是要做切割的,切完以后会把切割完的裸芯片重新配置到晶圆上,这块晶圆是为了做封装的专门的晶圆,为什么叫晶圆级封装?就是在晶圆片上进行封装,封装完以后再做一次切割,相当于两次切割,上图是Fan-out wafer level package的工艺流程。

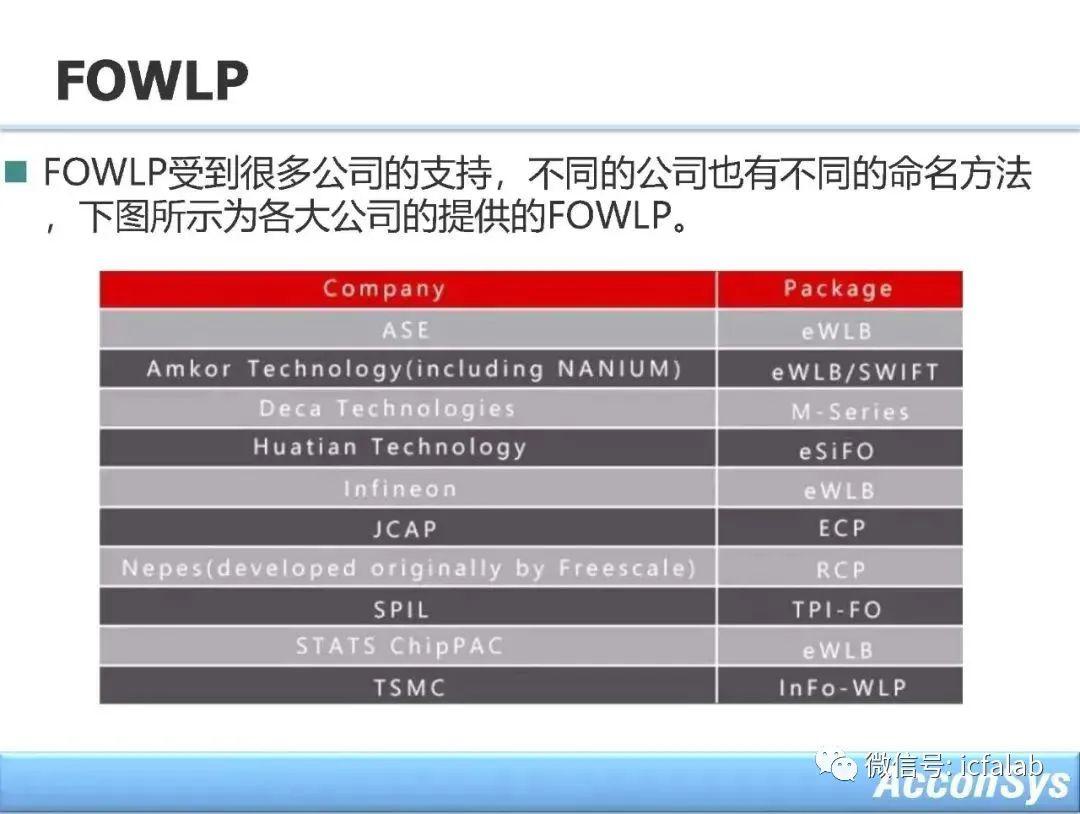

现在很多厂家,包括ASE、Amkor、华天在内,做封装的,英飞凌等,都在研究这种技术,各家公司的叫法不一样,虽然名字不同,但实际上技术都是相差不多的。

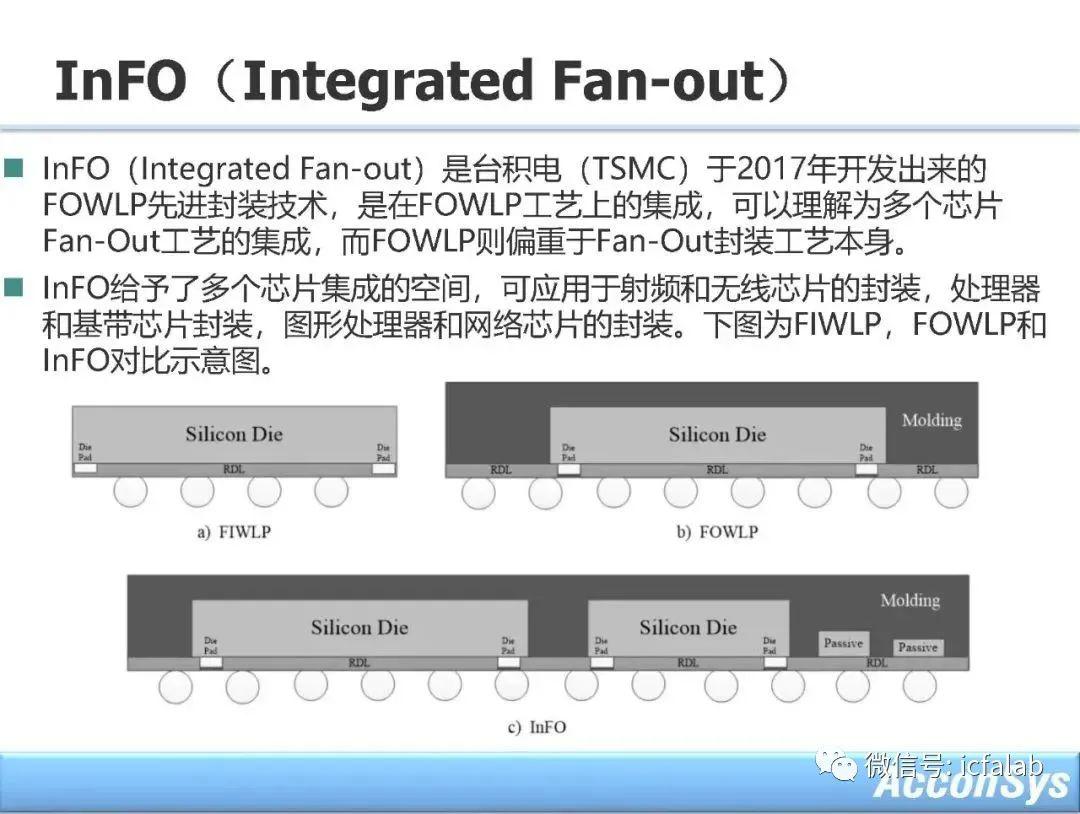

这里我们看看这种叫做INFO的技术,它叫做集成Fan-out,是台积电首创的。它把这个、上面两个,一个是Fan-in,一个是Fan-out,底下叫INFO,INFO它就是有集成的概念,所以叫做集成式Fan-out,它会把多个芯片通过这种Fan-out的技术给集成到一起,所以INFO可以认为是一种SiP,因为它是多芯片的,这个技术给台积电增加了很多很大的订单,促使台积电在先进封装领域进一步发力。

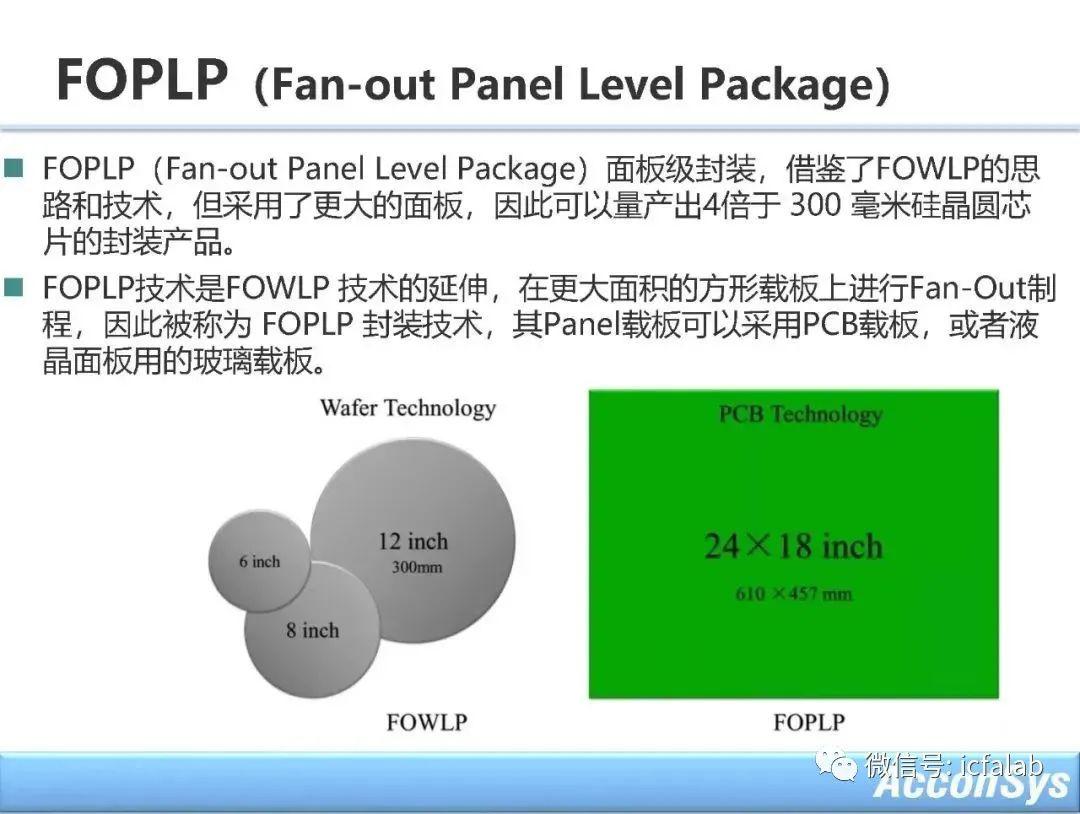

下面我们了解一下Panel level package,这是三星推出的,三星看见台积电出了INFO把订单抢走,也有点着急,就推出了Panel level package的工艺,它的工艺跟 Fan-out wafer level package有点像,但它的面板比较大,绿色的是它的面板、PCB技术, Wafer level package用的是晶圆技术,所以Panel level package的面板可以比它大4倍,这样的话生产效率就更高,虽然生产效率更高,但精度实际上还达不到 Fan-out Wafer level的水平,这是三星主推的一种先进封装技术。

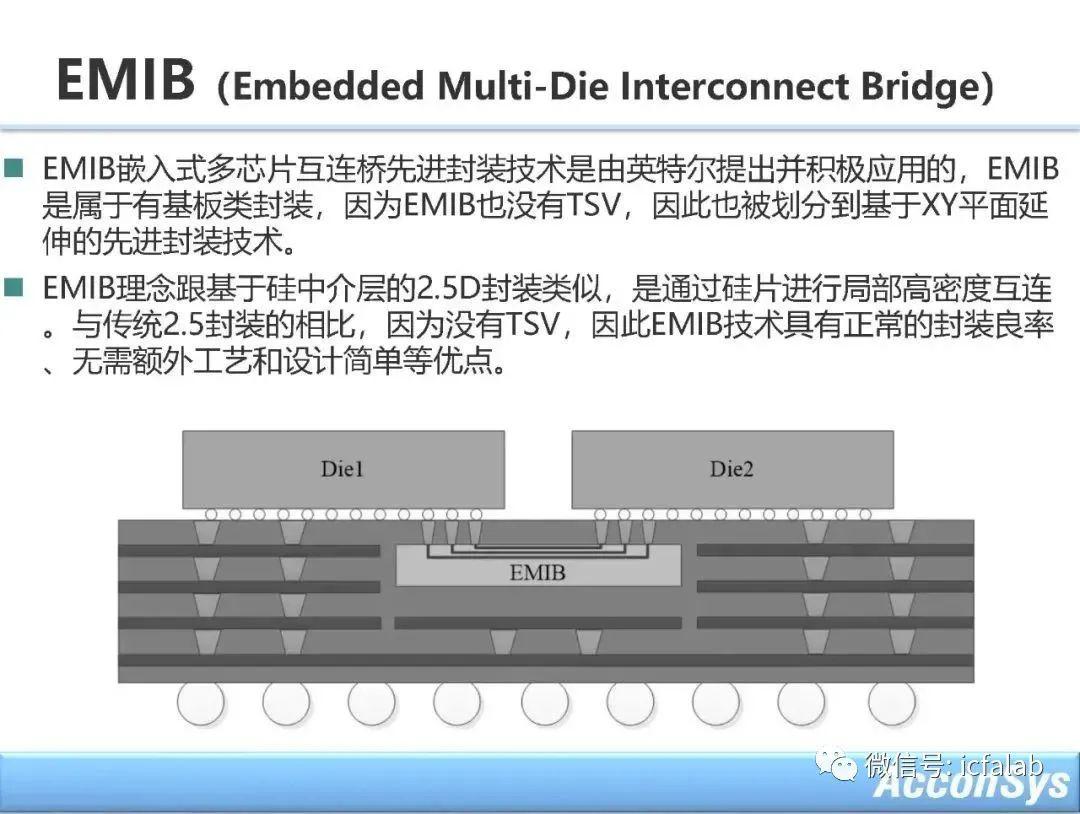

三星推出相应的解决方案后,其他的厂商也不甘落后,英特尔推出了EMIB嵌入式多芯片互连桥,EMIB是什么样的技术?就是说在芯片密度比较大的地方、连接比较密集的地方,嵌一块硅片,嵌到基板里,然后在硅上进行互连,这样的互连密度会很高,就像桥接一样,把它桥接起来。

EMIB是有硅材料互连的,有点像2.5D,但他们说比2.5D成本要低,灵活度更高,实际上是一种2D技术,不是2.5D。目前来说,英特尔在主推EMIB技术。

刚才讲了Fan-in、Fan-out、Fan-out Wafer,下面讲讲Z轴方向的延伸。

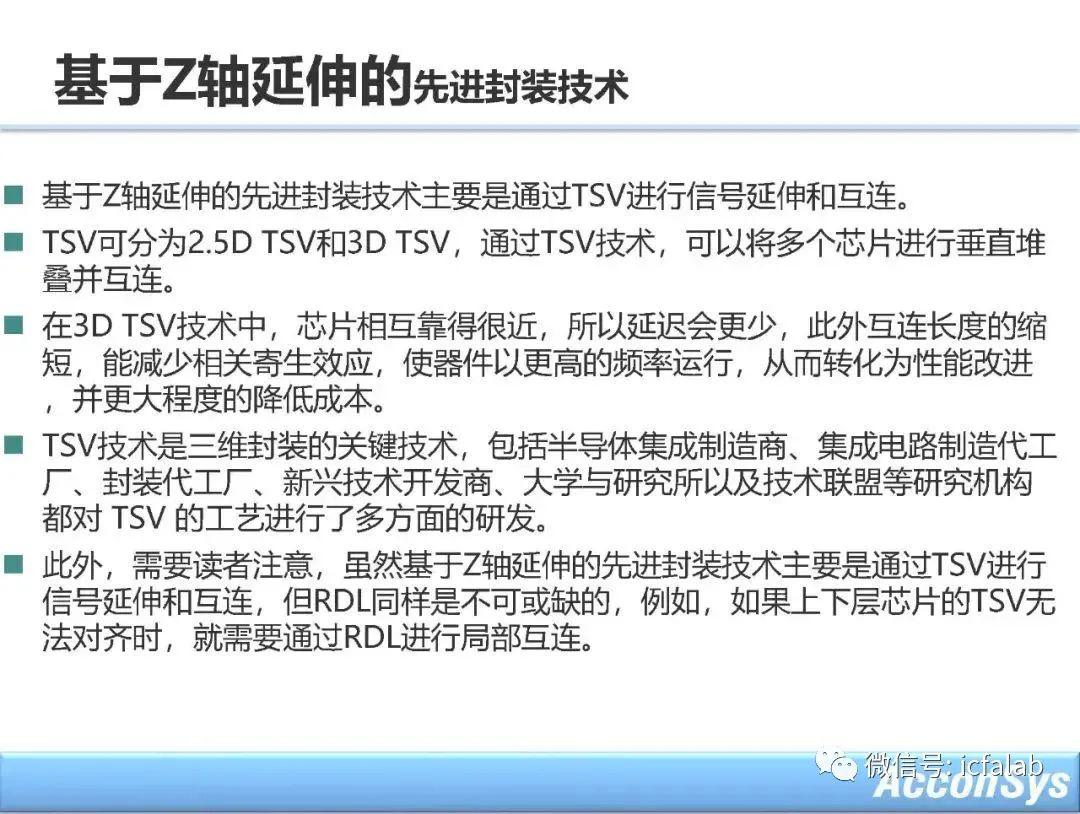

实际上先进封装的最大的特点就是可以做Z轴延伸,信号和器件都可以做Z轴延伸,就是往堆叠,Z轴延伸主要是通过TSV,刚才讲TSV是以后发展的非常重要的技术,TSV分为2.5D TSV和3D TSV,通过TSV技术,可以将多个芯片进行垂直堆叠并互连。

在3D TSV里面,芯片靠得非常近,延迟会很小,器件可以以更高的频率运行,从而转化为性能改进,降低成本。

目前技术上可以实现一平方毫米100万个TSV,密度非常高,沿着这个方向发展,以后TSV工艺势必会和晶圆制造、芯片制造融合到一起。

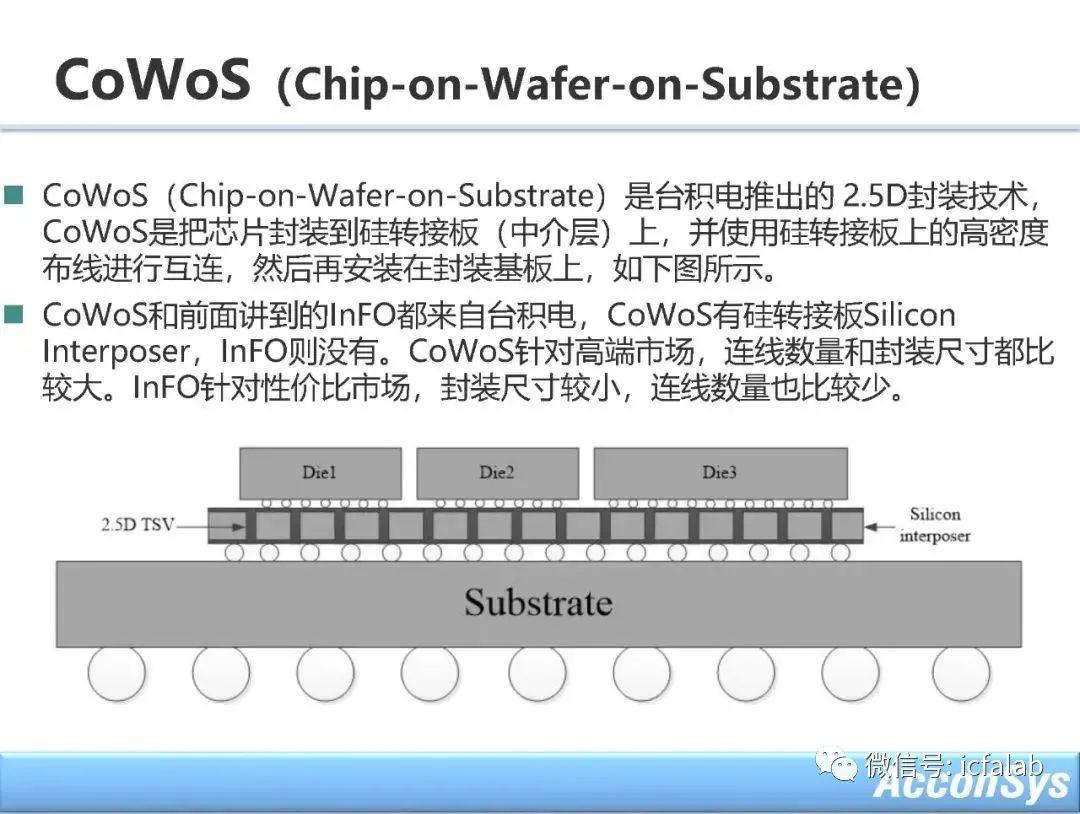

这个是台积电有名的CoWoS(Chip-on-Wafer-on-Substrate)工艺,实际上就是在基板和芯片中间加了一层硅中介板,这个是2.5D的,因为它有2.5D TSV,在硅中介板上有打孔,这与直接向锡板上安装的芯片有什么区别呢?它可以提高密度,CoWoS的互连密度可以很高,因为跟芯片的制造工艺很像,线都是以微米级甚至更小尺寸的线宽,这样密度会非常高,所以CoWoS和INFO的话,一个是面向高端市场,一个是面向低端、性价比市场,所以手机里面用得最多的实际上是INFO。

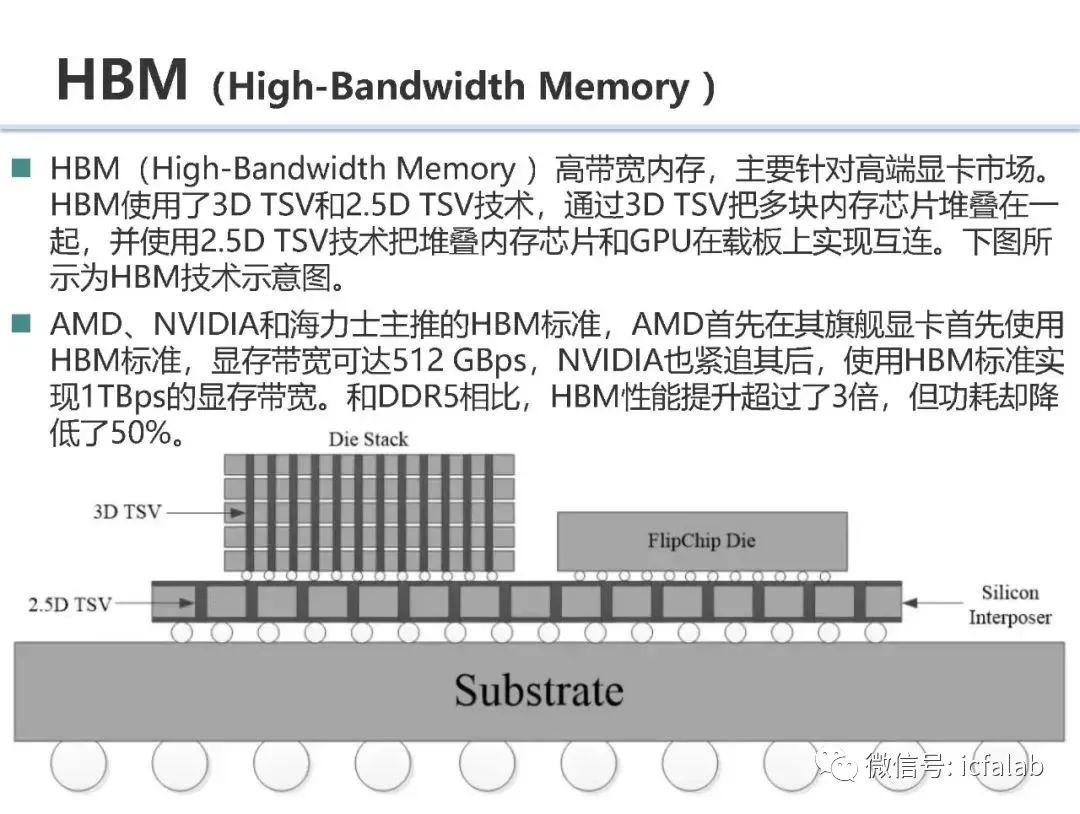

HBM(高带宽内存)是当前行业内比较红的产品,高带宽内存经常和DDR5相比,HBM的性能比DDR5高三倍,但功耗只有50%,这就很厉害了。

HBM就是将多块内存芯片给堆叠起来,通过硅通孔上下串起来,底下有逻辑控制器件,然后把它又和Flip Chip芯片或者一般的GPU通过2.5D的硅中介板集中在一起,我们看图可以发现,HBM的结构实际上比较复杂,这里面有3D TSV还有2.5D TSV,大概有几百,HBM可以称得上是集大成者,各种技术都有应用。

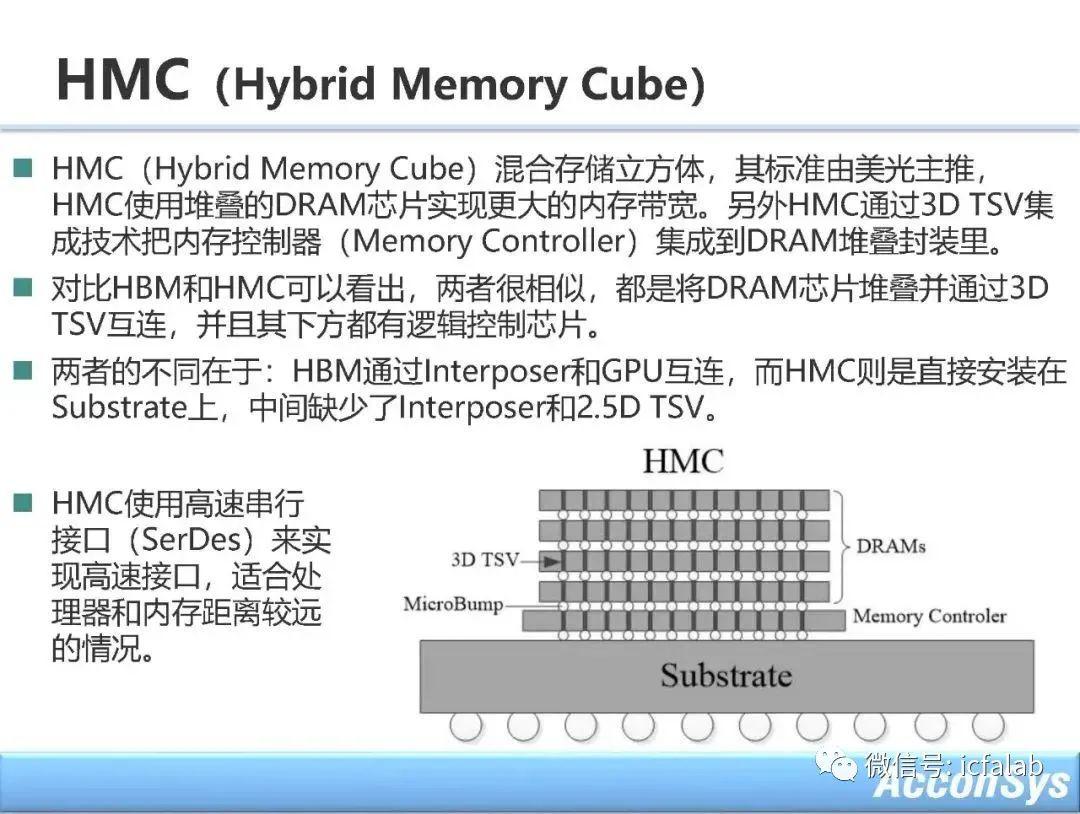

还有一种叫做HMC(混合存储立方体),HMC和HBM长得非常像,但是实际上仔细看的话不难看出它们之间的区别,HMC没有硅中介板,没有中间2.5D,通常有4个DRAM,底下有个控制器,都是通过3D TSV互连,但是它没有2.5D,而且HMC主要应用在服务器等领域。

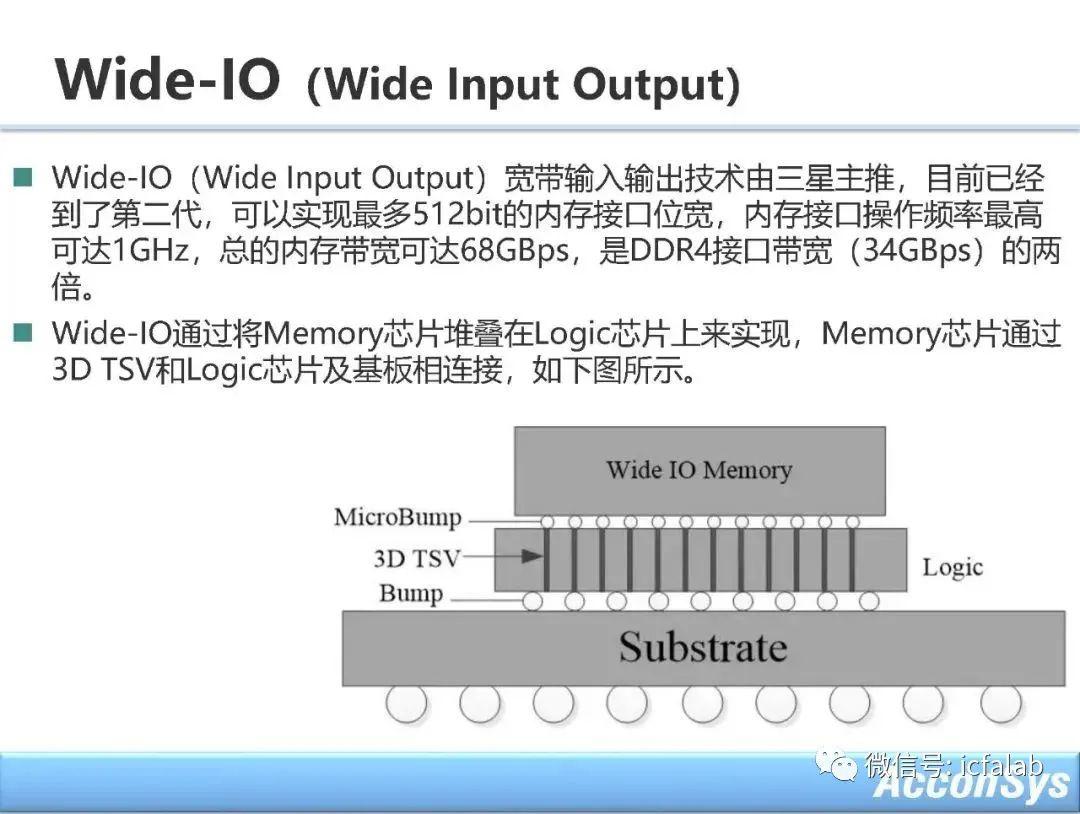

Wide-IO(宽带输入输出技术)主要由三星在推,是将Memory放在逻辑芯片上,通过3D TSV连接起来,也是3D的集成。

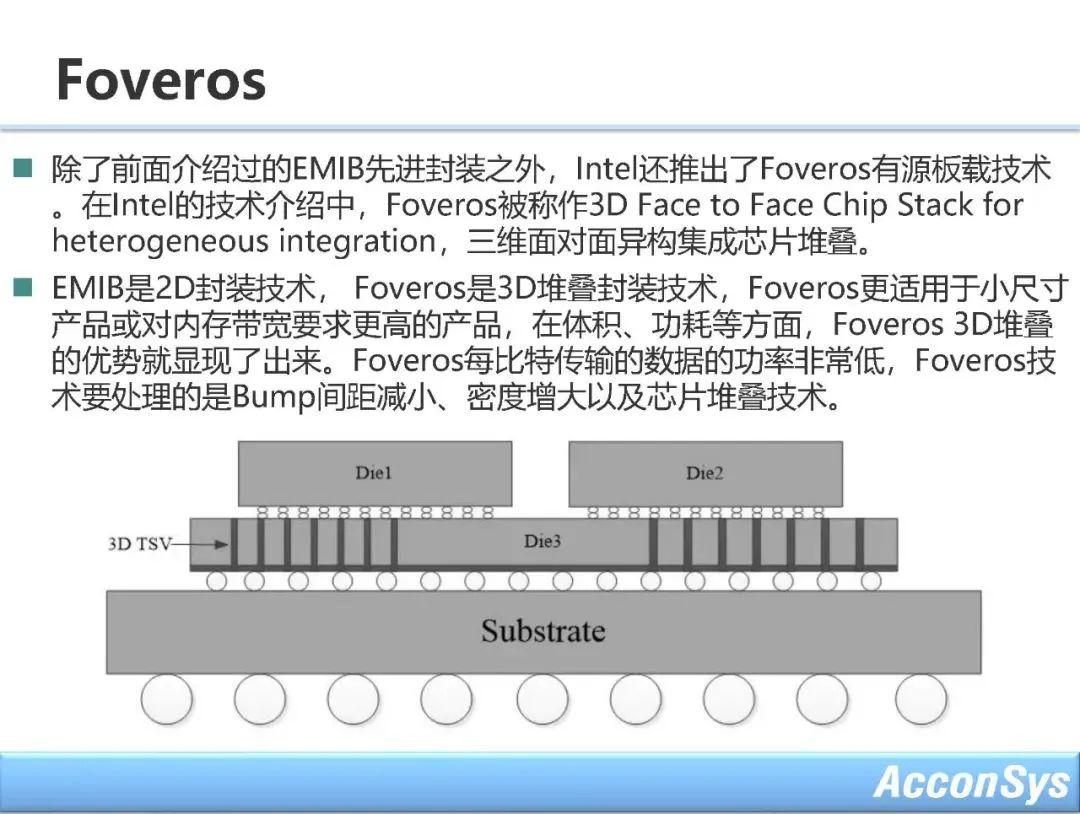

这里讲一讲英特尔的Foveros有源板载技术,它跟Wide-IO很像,底下是芯片,在芯片上打孔,芯片上面再摞芯片,通过TSV实现芯片之间的互连以及芯片和基板之间的互连,英特尔的3D Foveros和2D EMIB相当于组成了高低搭配。

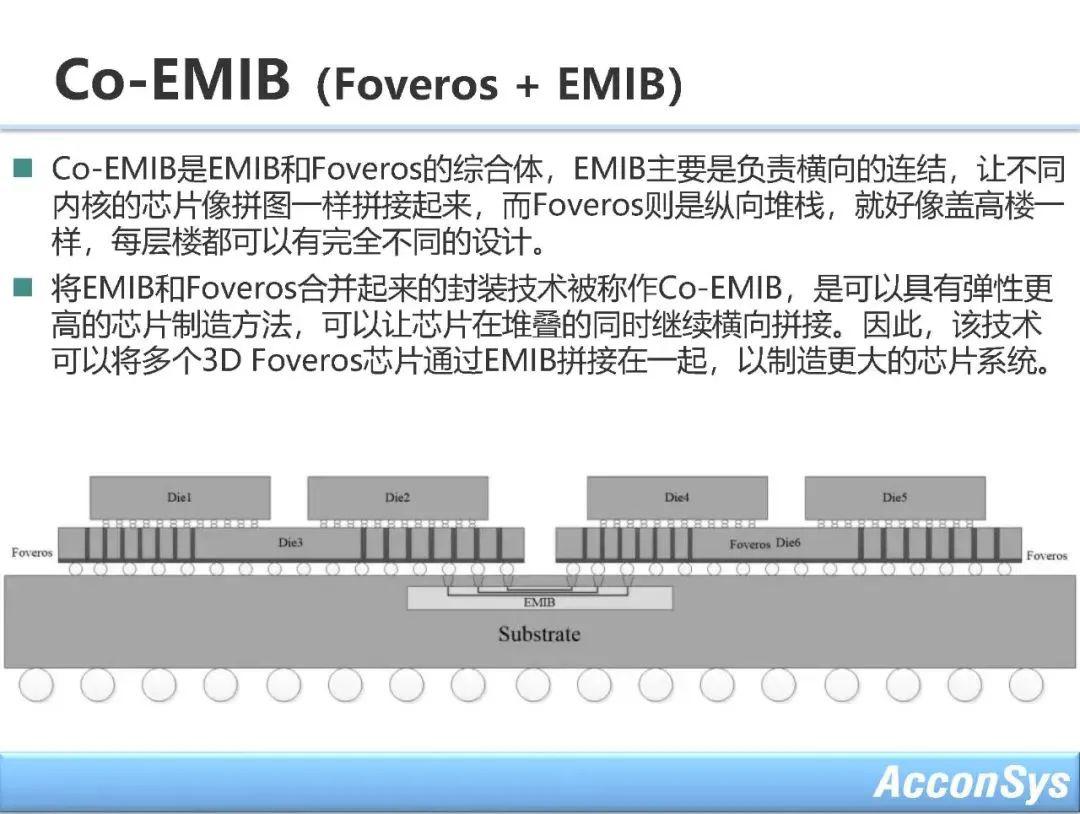

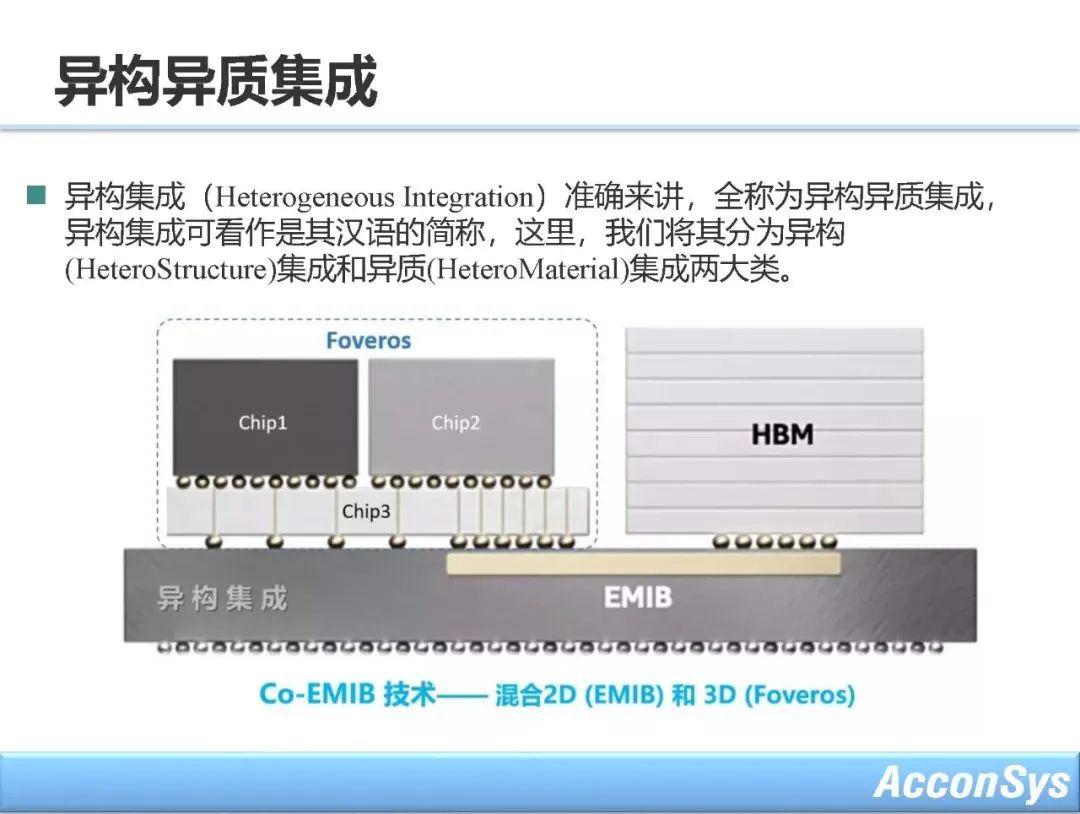

将Foveros和EMIB这两种技术结合在一起,就叫Co-EMIB技术,它是一种综合体,先通过Foveros集成以后,再通过EMIB把它们再做一次集成,这样的话就既有水平集成,又有垂直集成,于是可以制造出更大的芯片系统。英特尔现在也在做混合键合,没有凸点,但它现在的先进封装里大多数还是有凸点的。

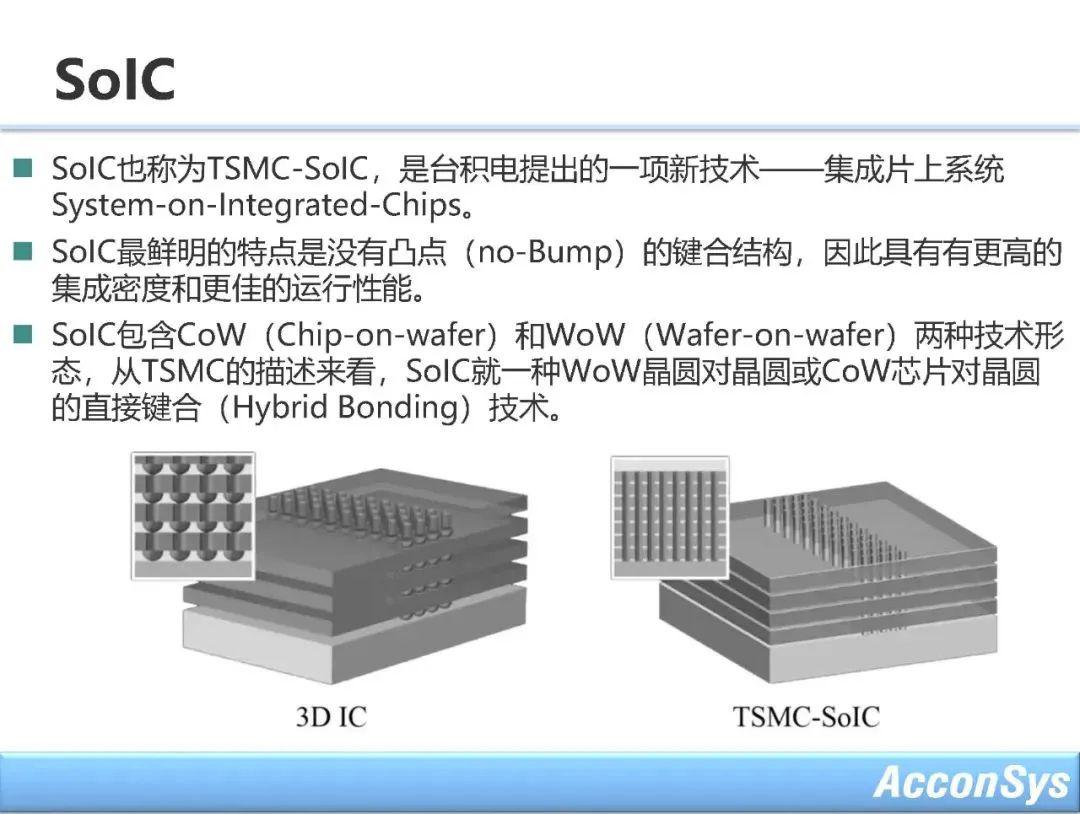

SoIC的话是台积电的一项新技术,这个它就提到了,没有凸点,没有Bump这样的结构,所以 SoIC右边这个可以看到,就是硅通孔上下直接串起来没有凸点,像左边这样的凸点,没有凸点的话它这个密度会更高,互连会更近,这是以后发展的趋势,先进封装最后都会走到这一步。

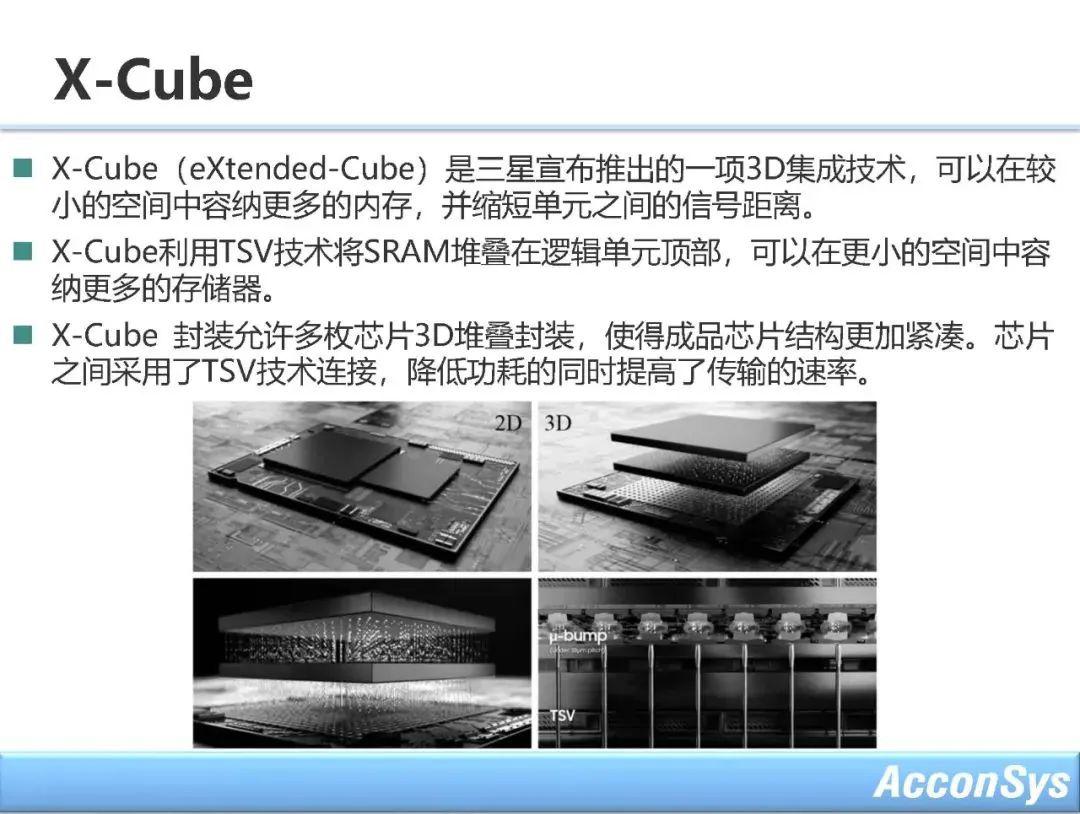

还有一个叫X-Cube,这是三星推出来的,这个我没有看出来它有什么别具一格的特色,它也是通过3D TSV堆叠。

由于时间关系我不深入解析,接下来,我们对刚刚聊到的这些先进封装技术做一个小结。

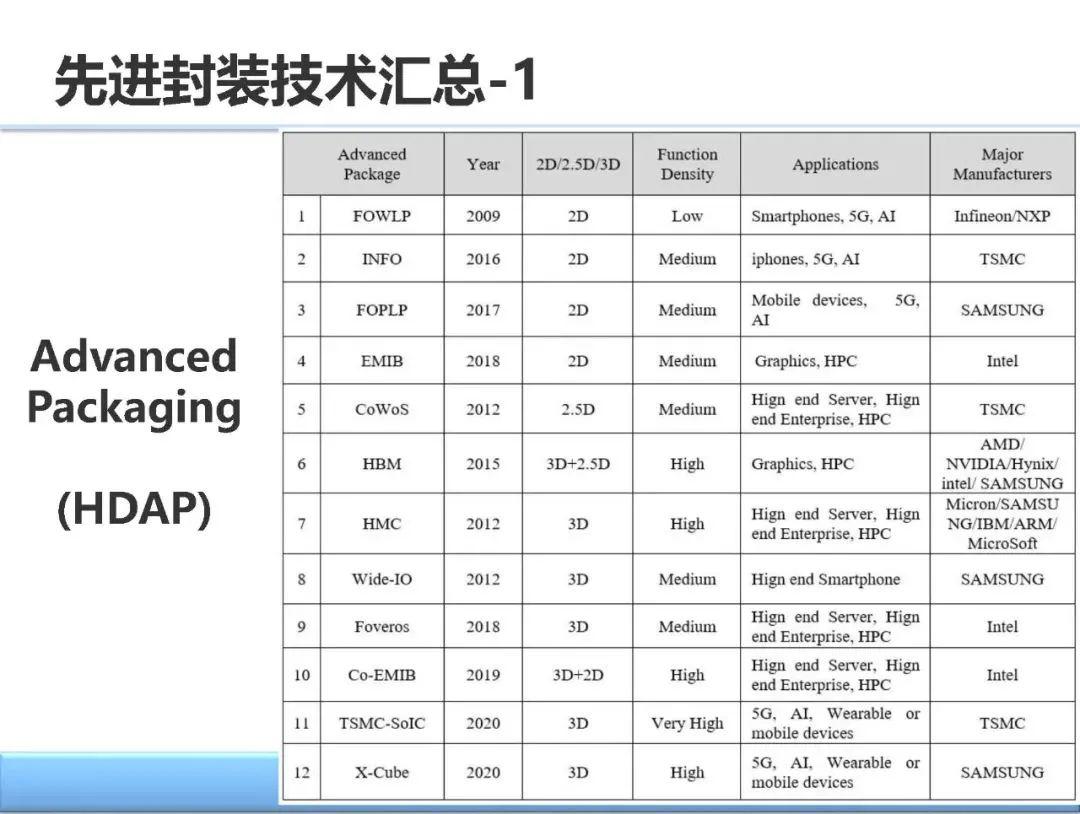

大家看一下这张表,表中列举了刚刚我讲到的12种先进封装技术,不同的厂家、推出的时间、功能密度及它们的技术特性。

之前我们进行过分类,晶圆级封装、面板级封装、2.5D封装和3D封装,大家看这里的结构图就能看得非常清楚,这12种先进封装技术各自是属于哪一类。

最后我们来讲一讲异构集成。

咱们现在理解的芯片都叫单片集成,它是同构的,意思就是说在同一种材料上做出所有的元件,电阻、电容、晶体管,1958年,基尔比发明了世界上第一款集成电路,四十二年以后,他获得了2000年的诺贝尔奖。

异构集成的概念就不一样,准确来说,异构集成的全称应该是异构异质集成,异构主要指的是工艺节点不同,而异质指的是材料不同。

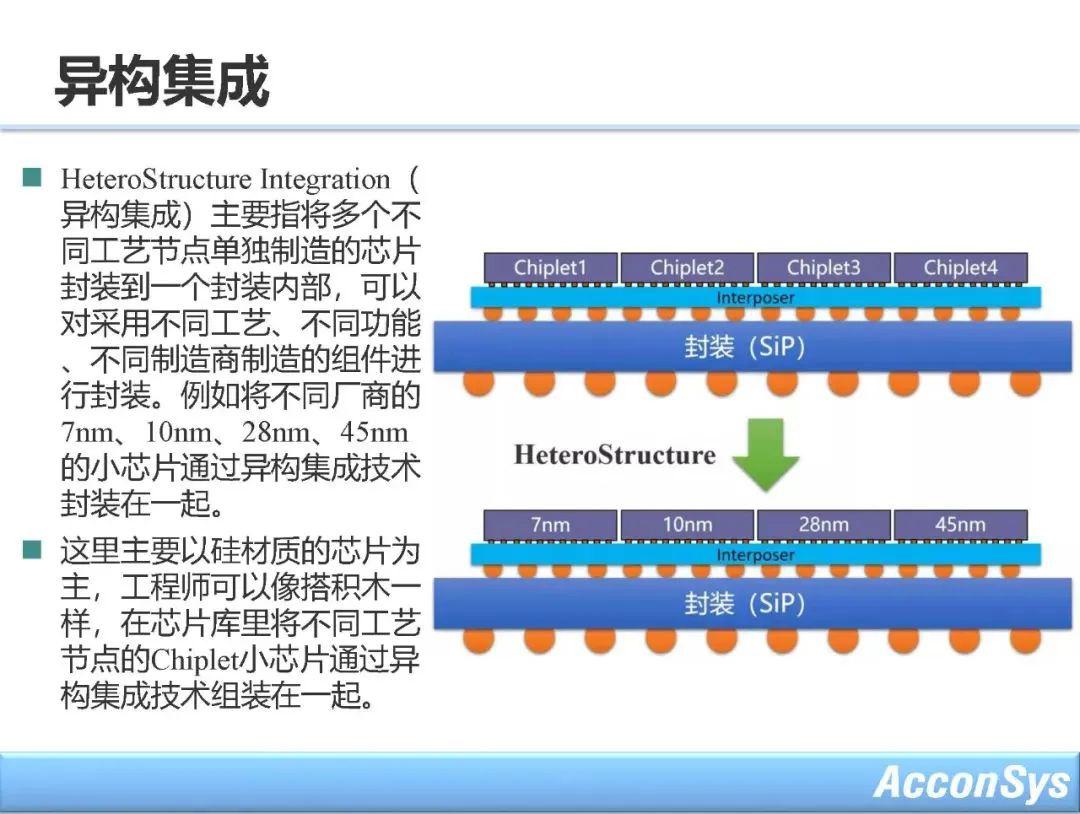

异构集成就是说,我们看到芯片集成在一起的时候,如果是一个芯片的话,你必须采用比如说28纳米或者是10纳米,如果是异构的话,我可以把7纳米、10纳米、28纳米、45纳米集成在一起,因为它的集成度非常高,跟芯片接近,所以我们把它称为异构集成,这就是Chiplet的概念,先把它划分出来,然后用不同的工艺节点去制造,然后再集成在一起,这叫异构集成。

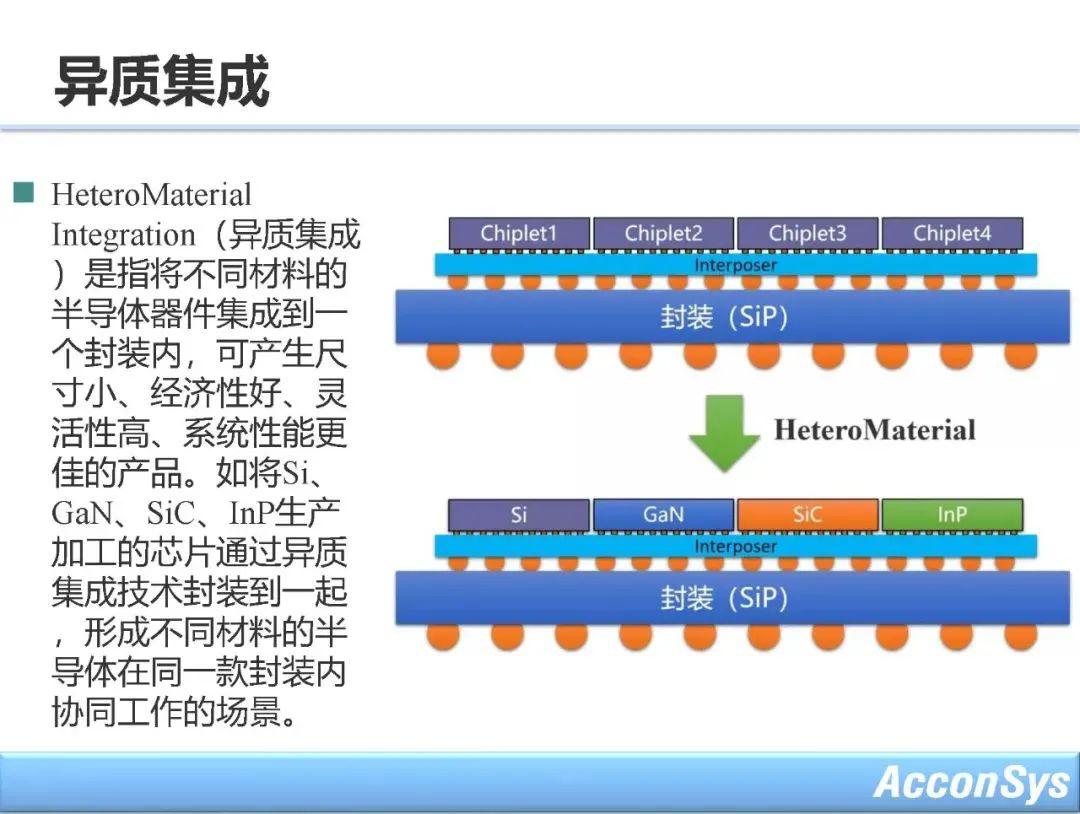

另外一种就是异质集成,就是说我除了采用不同的节点以外,我还可以采用不同的材料,大家知道现在半导体除了硅以外,还有很多其它的像氮化镓、碳化硅、磷化铟等其它材料,当然其它材料主要还是用在一些特殊领域,什么功率半导体啦、什么射频滤波啦,数字电路大都是以硅为主,这样的话可以在封装内把不同的材料集成在一起,就叫异质集成。

最后我们说说异构集成和小芯片。

Chiplet,就是小芯片,这个现在比较流行,它是先将复杂的功能分解、开发出能解决单一问题的小芯片,类似系统的子模块,然后再像搭积木那样把小芯片封装在一起。大家看这张图吧。

单片就是SoC,我做一个SOC,大家知道,它的面积很大,复杂程度很高,所以验证的时间也比较长,而且容易出现缺陷。另外一种思想就是SiP,我把它分成几块,做成不同的芯片,然后在封装体内集成这个SiP,Chiplet比SiP更进了一步,我可以分得更小,把每个IP都做成小芯片,然后再把它封装体内集成。

Chiplet可以把每个IP、SiP里面有很多IP对吧,我把每个IP都做成一个小芯片,然后再去给它集成,所以从这个图里大家知道SoC、SiP和Chiplet之间的关联以及区别。

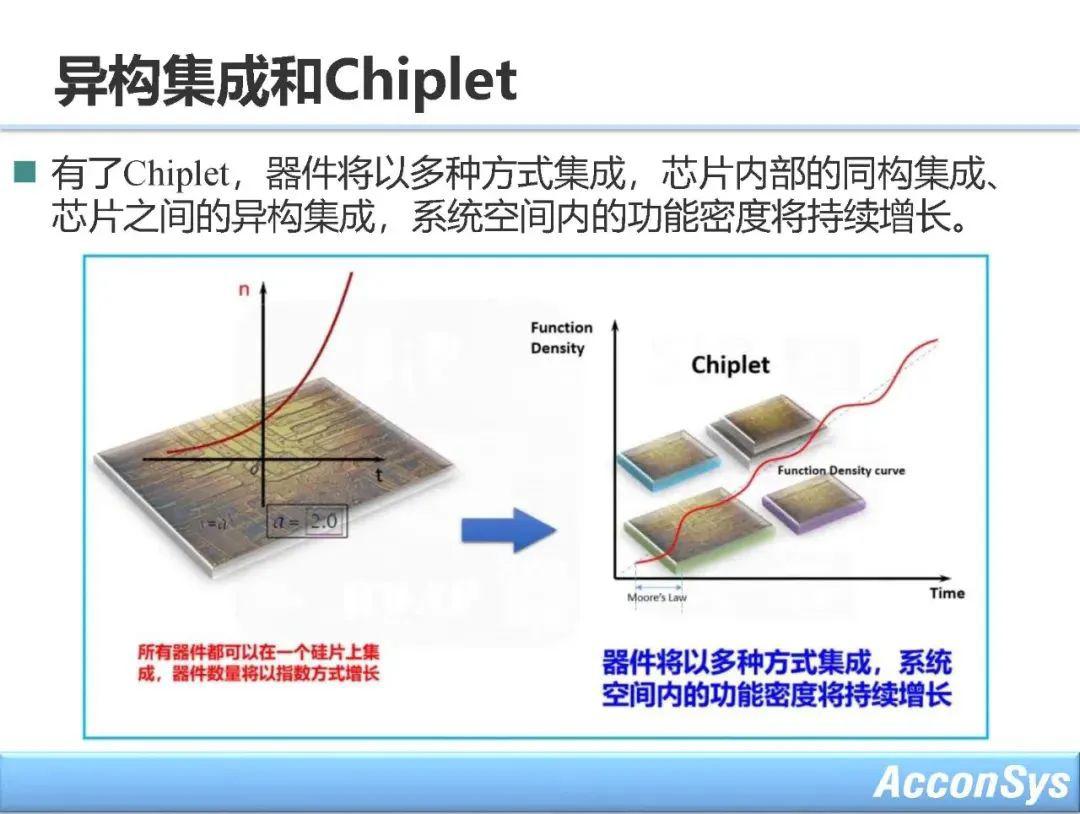

异构集成跟同构集成是不一样的,按照摩尔定律,芯片上晶体管的数量增长是翻倍的,翻倍的话实际上是指数曲线,这个指数曲线我一直说,它实际上是不可持续的,所以到了Chiplet的异构集成地带,它的功能密度还会增加,但不会以这种指数曲线的形式增加。

另外讲一个概念,就是异构计算,这里一起给大家讲一下。

我们有一次参加研讨会,当时大家一起讨论了一个概念叫做异构时代,什么叫异构时代呢?实际上异构时代就是包括了异构集成和异构计算的时代。

异构计算主要是在软件方面,包括CPU、GPU、FPGA、DSP等不同架构的运算单元,将它们整合在一起进行计算,按照谁擅长谁来做的原则,GPU、FPGA、DSP、CPU共同去完成计算任务,这就是异构计算。

关于异构计算和异构集成之间的关系,我画了一张图,异构计算在软件层面,而异构集成则是在硬件的封装层面,所以异构计算有些时候需要异构集成来协助,而通过异构集成的话,就更容易实现异构计算,比如说你可以把FPGA啦、CPU这些集中在一起。

大家看这里的总结,异构集成和先进封装技术扮演了关键角色,可以快速达到异构计算系统芯片所需要的功耗体积和性能要求。

赵工

13488683602

zhaojh@kw.beijing.gov.cn

欢迎各公众号,媒体转载,申请加白名单秒通过

投稿/推广/合作/入群/赞助/转发 请加微信13488683602