Q1

жңүдёӘй—®йўҳиҜ·ж•ҷдёҖдёӢеҗ„дҪҚеӨ§зҘһпјҢжү“ESDж—¶еҰӮжһңиҠҜзүҮеҶ…йғЁеј•еҮәзҡ„еӨҡдёӘз®Ўи„ҡиҝһйҖҡзҡ„пјҢжҳҜдёҚжҳҜеҸӘиҰҒжү“е…¶дёӯдёҖдёӘз®Ўи„ҡе°ұеҸҜд»ҘпјҢиҝҳжҳҜеҮ дёӘз®Ўи„ҡйғҪиҰҒжү“пјҹ

A

жҲ‘们д№ӢеүҚеҒҡиҝҮзұ»дјјзҡ„пјҢеҒҡеҺӢйҷҚжӢ“жү‘еҲҶжһҗпјҢеҺҹеҲҷдёҠе’ҢеҺӢйҷҚжңҖеӨ§е°ұеӨҹдәҶпјҢеҰӮжһңеҺӢйҷҚжңҖеӨ§зҡ„е’Ң第дёҖдёӘжІЎе•ҘеҢәеҲ«пјҢеҸҜд»ҘдёҚ用继з»ӯгҖӮ

Q2

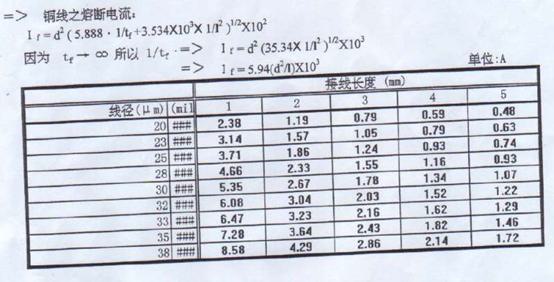

еҗ„дҪҚеӨ§е’–пјҢ и°ҒжңүCu wire bonding зҡ„иҝҮз”өжөҒеҸӮж•°иЎЁпјҢ0.8mil/0.9mil/1.0mil еҲҶеҲ«еңЁзәҝй•ҝжҳҜ1.5mm/2mm/2.5mmзҡ„иҝҮз”өжөҒпјҹ

A

еҸӮиҖғеҰӮдёӢпјҡ

Q3

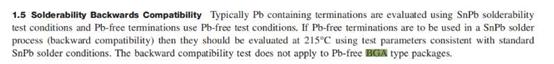

BGA packageиҠҜзүҮйңҖиҰҒ Solderability testеҗ—пјҹд»ҺJEDCж–Ү件дёӯжІЎжңүжҹҘиҜўеҲ°жӯӨж–№йқўзҡ„е®ҡд№ү

A

Q4

иҜ·й—®е·ҘиүәеҠ е·Ҙдёӯе…үеҲ»иғ¶еҸ‘з”ҹеҸҳжӣҙпјҢдә§е“ҒйңҖиҰҒеҒҡеҸҜйқ жҖ§йӘҢиҜҒеҗ—пјҹ

A

иӮҜе®ҡиҰҒзҡ„пјҢPRеұһдәҺдё»жқҗпјҢжӣҙжҚўеҜ№зәҝе®ҪеҪўиІҢйғҪжңүеҪұе“ҚгҖӮ

Q5

A

дёҖиҲ¬е»әи®®жҢүз…§жңҖWorst case зҠ¶жҖҒпјҢжүҖд»ҘйҖҡеёёжҢүз…§1.1еҖҚдёҠз”өжөӢиҜ•Latch up

Q6

жұӮй—®еҗ„дҪҚеӨ§дҪ¬пјҢжҳҜдёҚжҳҜInGaAsе’ҢOBIRCHзҡ„дёӨз§Қж–№жі•з»“жһңжҳҜдёҚдёҖж ·зҡ„пјҹжҜ”еҰӮиҜҙжҲ‘еҲҡејҖе§ӢжҳҜOBIRCHпјҢ然еҗҺдёӯй—ҙжҠҠеҮ ж №зәҝжҢ‘ж–ӯеҗҺпјҢеҶҚеҒҡдә®зӮ№еҒҡзҡ„InGaAsпјҢиҝҷж ·жҲ‘зҡ„еүҚеҗҺеҜ№жҜ”жңүж„Ҹд№үеҳӣ

A

зңӢdefectзұ»еһӢпјҢmetalй—ҙзҹӯи·ҜпјҢOBIRCHдёҖиҲ¬жҳҜеҸҜд»ҘжҳҺжҳҫзңӢеҲ°зҡ„пјҢеҰӮжһңжҳҜFEOLзҡ„й—®йўҳпјҢеӨ§еӨҡж•°з”ЁInGaAsпјҢдёҖдёӘзңӢйҳ»еҖјеҸҳеҢ–пјҢдёҖдёӘзңӢе…үеӯҗж•ЈеҸ‘жіўй•ҝиғҪйҮҸпјҢеҸҜеҸӮиҖғиЎЁж јпјҡпјҲиЎЁдёӯmmж”№жҲҗumпјү

Q7

иҜ·ж•ҷдёҖдёӘй—®йўҳпјҡжҲ‘们зҺ°еңЁз”Ёзҡ„ж–°е“ҒпјҢpadйЎ¶еұӮжҳҜ10umзҡ„еҺҡй“ңгҖӮдё»иҰҒжҳҜдёәдәҶйҷҚдҪҺеӨ§з”өжөҒж—¶еҖҷзҡ„йҳ»жҠ—гҖӮиҝҷз§Қжғ…еҶөдёӢзҡ„з»“жһ„пјҢжҳҜеҗҰиҝҳиғҪеӨҹз”ЁжқҘиҝӣиЎҢе°ҒиЈ…зҡ„жү“зәҝпјҹе°ҒиЈ…жҳҜLQFP64зҡ„е°ҒиЈ…гҖӮ

A

еҺҡй“ңpadжІЎжңүеҠһжі•жү“зәҝпјҢеҸҜеҒҡиЎЁйқўеҢ–й•ҖNiPdAuеӨ„зҗҶпјҢд№ӢеҗҺWBгҖӮ

Q8

A

ж¶Ҳиҙ№зұ»з”өеӯҗ>=95%пјҢиҪҰ规зә§>=95%

Q9

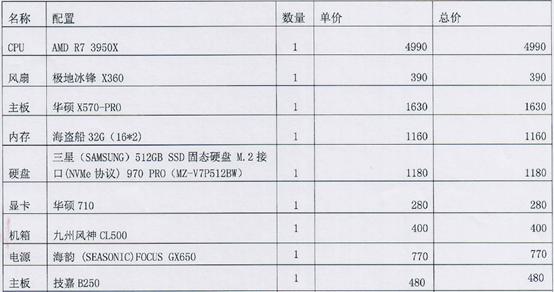

иҜ·й—®дёӢ CP/FT ж•°жҚ®еҲҶжһҗзҡ„еҸ°ејҸжңәпјҢжңүжІЎжңүе»әи®®зҡ„й…ҚзҪ®е‘ҖпјҹеӨҡж ёиҝҳжҳҜеә”иҜҘеӨ§еҶ…еӯҳпјҹзӣ®зҡ„пјҡжөӢиҜ•ж•°жҚ®еӯҳжЎЈпјӣжөӢиҜ•ж•°жҚ®еҝ«йҖҹеҲҶжһҗпјҢжӢүеӣҫиЎЁзӯүдҪҝз”ЁпјӣеҪ“еүҚжғ…еҶөпјҢе°Ҹе…¬еҸёеүҚеҮ е№ҙиҝҮеәҰдҪҝз”ЁгҖӮдёҚзҹҘйҒ“иҝҷдёӘй…ҚзҪ®еҠ дёӘNAS жңәжў°зӣҳжҳҜдёҚжҳҜе°ұеҸҜд»ҘдәҶгҖӮ

A

CPUе»әи®®з”Ё5950XпјҢSSDе°ҸдәҶпјҢжңҖдҪҺд№ҹиҰҒ1TBе•ҠгҖӮиҝҷйҮҢдёҚе»әи®®NASпјҢдёҚеҗҲйҖӮгҖӮNASйҖӮеҗҲзҪ‘з»ңдј иҫ“гҖҒеӨ§е®№йҮҸпјҢдҪҺйҖҹеәҰгҖӮдҪ йғҪжһ¶еҸ°ејҸжңәдәҶпјҢзӣҙжҺҘеңЁйҮҢйқўж”ҫRAIDе°ұеҘҪдәҶе•ҠгҖӮ

Q10

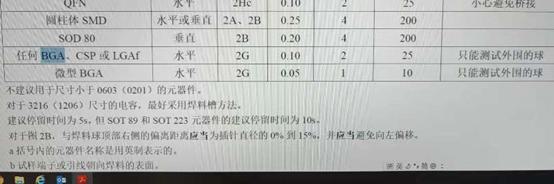

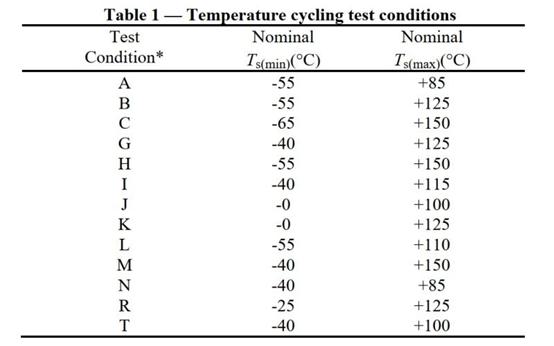

иҜ·ж•ҷдёӢеҗ„дҪҚеӨ§дҪ¬пјҢйҷ¶з“·е°ҒиЈ…дёҖиҲ¬еҒҡе“ӘдәӣеҸҜйқ жҖ§йЎ№зӣ®пјҹ

A

йҷ¶з“·е°ҒиЈ…еҸӮAECQж ҮеҮҶйғҪжңүиҜҰз»ҶиҜҙжҳҺпјҢдёҚдёҖе®ҡжү§иЎҢеҶ…йғЁжөӢиҜ•жқЎд»¶пјҢйҷ¶з“·е°ҒиЈ…еҸӮиҖғAECQж ҮеҮҶжңүиҜҰз»ҶиҜҙжҳҺпјҢдёҚдёҖе®ҡжү§иЎҢеҶ…йғЁжөӢиҜ•жқЎд»¶пјҢеҸҜйқ жҖ§еҲҶдёә test item е’Ң test conditionпјҢtest itemеҸҜд»ҘеҺ»еҸӮиҖғ AECQж ҮеҮҶйғҪеҸҜд»ҘжҹҘеҲ°пјҢconditionж №жҚ®дҪҝз”ЁзҺҜеўғеҒҡи®ҫи®ЎгҖӮ

Q11

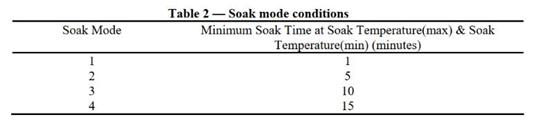

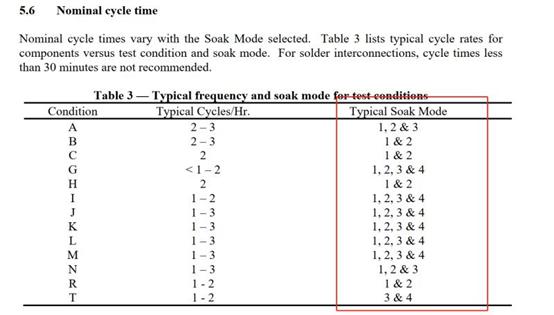

иҜ·й—®дёӢпјҡJESD22-A104дёӯй«ҳдҪҺжё©зҡ„еҒңз•ҷж—¶й—ҙеҰӮдҪ•йҖүжӢ©е‘ўпјҹ

A

Q12

иҜ·ж•ҷеӯЈдё°дёӘй—®йўҳпјҡеңЁи®ҫи®ЎBIBжҲ–иҖ…FT LBж—¶пјҢжңүж•ҲйҷҚдҪҺPowerдә§з”ҹзҡ„еҜ„з”ҹз”өж„ҹйғҪжңүе“ӘдәӣжүӢж®өпјҹжҜ”еҰӮ3mmеҺҡзҡ„PCBжқҝдёҠеҚ•дёӘviaдә§з”ҹзҡ„еҜ„з”ҹз”өж„ҹдёҖиҲ¬еӨ§жҰӮжҳҜеӨҡе°‘пјҹ

A

1гҖҒ еўһеӨ§viaпјҢжҜ”еҰӮйҮҮз”Ё20milзҡ„viaгҖӮ

2 гҖҒйҮҮз”Ёvia on padжҠҖжңҜгҖӮе°ұжҳҜжҠҠviaзӣҙжҺҘжү“еңЁз”өе®№зҡ„padдёҠ

3 гҖҒж•ҙзүҮй“әең°пјҢеӨ§йҮҸжү“еӯ”пјҢз”ЁplaneжҠҠviaиҝһжҲҗдёҖзүҮгҖӮ

Q13

еҗ„дҪҚеӨ§зҘһBGAиҠҜзүҮеҒҡBHASTж №жҚ®и§ӮеҜҹжҳҜз®Ўи„ҡж°§еҢ–дёҘйҮҚпјҢжөӢиҜ•FTејӮеёёеӨҡпјҢдёҖиҲ¬жңүд»Җд№Ҳи§ЈеҶіж–№жЎҲеҗ—пјҹ

A

800з Ӯзәёи№ӯеҮ дёӢпјҢи№ӯе®Ңд№ӢеҗҺеҶҚз”Ёй…’зІҫж№ҝеёғжё…жҙҒдёҖдёӢпјҢйҒҝе…ҚжҺүиҗҪзҡ„зІүзЈЁжұЎжҹ“socket pogopinгҖӮ

Q14

иҜ·й—®дёӢеӯЈдё°зҡ„еӨ§дҪ¬д»¬пјҢеҒҡSERйӘҢиҜҒдёҖиҲ¬жҳҜз”ЁиЈёdieиҝҳжҳҜе°ҒиЈ…зүҮе‘ўпјҹ

A

е°ҒиЈ…иҠҜзүҮ

Q15

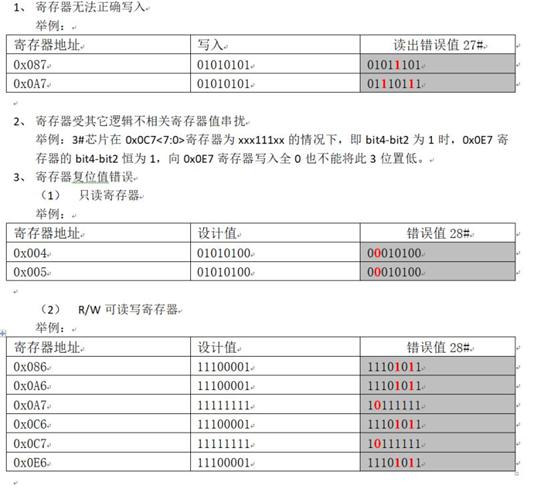

зҫӨйҮҢзҡ„еӨ§е’–们й’ҲеҜ№еҰӮдёӢзҡ„й—®йўҳиғҪеҗҰеё®еҝҷжҸҗдҫӣеҲҶжһҗжҖқи·Ҝпјҹ

A

д»Һж•°жҚ®зңӢпјҢrepeatеҫҲзЁіе®ҡпјҢй”ҷиҜҜbit并没жңүй”ҷдҪҚзҡ„规еҫӢпјҢжҸҗдҫӣдёӨз§ҚжҖқи·ҜиҜ•дёҖдёӢ

1.ж”№еҸҳdigital powerз”өеҺӢиҜ•дёҖдёӢиҜ»default regзҡ„еҖјжҳҜеҗҰйғҪеҸҳеҢ–пјҢ

2.еҶ·еҮқеүӮе–·дёҖдёӢиҠҜзүҮпјҢзңӢзңӢеӣһиҜ»еҖјжҳҜеҗҰжңүеҸҳеҢ–пјҢtimingй—®йўҳдёҖиҲ¬е’Ңжё©еәҰејәзӣёе…і

Q16

еҗ„дҪҚеӨ§зҘһпјҢеҹәжқҝе°ҒиЈ…е’ҢMISжЎҶжһ¶е°ҒиЈ…зҡ„дјҳзјәзӮ№жҳҜд»Җд№Ҳпјҹ

A

MISзӣ®еүҚеҸҜд»ҘеҒҡ1-2еұӮпјҢ4*4д»ҘдёӢзҡ„еҸҜйқ жҖ§жҜ”иҫғеҘҪгҖӮжҲҗжң¬зӣёеҜ№дәҺеҹәжқҝдҫҝе®ңгҖӮ

жқҘжәҗпјҡеӯЈдё°з”өеӯҗ

иөөе·Ҙ

13488683602

zhaojh@kw.beijing.gov.cn

ж¬ўиҝҺеҗ„е…¬дј—еҸ·пјҢеӘ’дҪ“иҪ¬иҪҪпјҢз”іиҜ·еҠ зҷҪеҗҚеҚ•з§’йҖҡиҝҮ

жҠ•зЁҝ/жҺЁе№ҝ/еҗҲдҪң/е…ҘзҫӨ/иөһеҠ©/иҪ¬еҸ‘ иҜ·еҠ еҫ®дҝЎ13488683602