Q1

QFNе°ҒиЈ…еҮәиҙ§пјҢе®ўжҲ·иҰҒжұӮжөӢиҜ•еүҚ100% reflowжҳҜеҗҰеҗҲзҗҶзҡ„пјҢжҲ–иҖ…жҷ®йҒҚиҝҷд№ҲиҰҒжұӮпјҹиҝҳжҳҜжҲ‘们еҜ№д»–зҡ„иҰҒжұӮзҗҶи§Јзҡ„дёҚеҜ№пјҢд»–иҝҷжҳҜеҜ№еӣһжөҒз„ҠеҠ е·Ҙж—¶зҡ„иҰҒжұӮпјҹ

A1

дёҖиҲ¬е·ҘеҺӮжңүиҝҷдёӘжңҚеҠЎзҡ„пјҢеңЁPMCд№ӢеүҚеҸҜд»ҘеўһеҠ 100%reflowзҡ„еҠЁдҪңпјҢдё»иҰҒжҳҜLGAзұ»дә§е“ҒеңЁPMCд№ӢеҗҺиҝӣиЎҢдёҖж¬ЎreflowпјҢжҸҗеүҚжҝҖеҸ‘е…ғеҷЁд»¶еә•дёӢдёІй”ЎгҖҒdelamзӯүејӮеёёпјӣQFNеҒҡиҝҷдёӘзҡ„иҜқпјҢreflowеҸӮж•°иҝҳиҰҒзңӢдёӢпјҢеҸҜиғҪдә§з”ҹй”Ўйј“иҝҷдәӣй—®йўҳгҖӮ

Q2

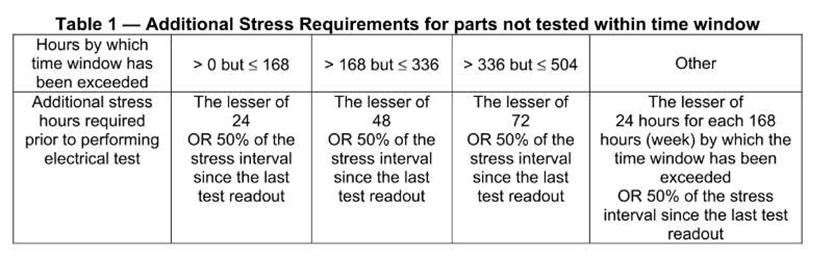

иҝҷдёӘиЎЁж јдёӯ第дёҖж ҸпјҢжҳҜHTOLеҒңжӯўзҡ„ж—¶й—ҙиҝҳжҳҜе·Іе®ҢжҲҗзҡ„ж—¶й—ҙпјҹ

A2

еӣһжөӢзҡ„ж—¶й—ҙгҖӮ

Q3

WLCSPеӣ дёәйғҪжҳҜз ”зЈЁеҲҮеүІеүҚжөӢиҜ•зҡ„пјҢйӮЈд№Ҳд№ӢеҗҺprocessеј•е…ҘиҖҢAOIжЈҖжөӢдёҚеҲ°зҡ„дёҚиүҜжҜ”дҫӢпјҹиҝҷдёӘйңҖиҰҒе·ҘеҺӮзҡ„еӨ§ж•°жҚ®жүҚиЎҢгҖӮ

A3

дёҖиҲ¬жҳҜ6SжЈҖжҹҘ AOIи®ҫеӨҮпјҢй«ҳзІҫеәҰзҡ„CCDзӣёжңәжҺўжөӢпјҢеҸҰеӨ–жңүдәӣFabз”ЁIRжҳҫеҫ®й•ңиҝӣиЎҢжЈҖжҹҘпјҢд»ҺиҠҜзүҮиғҢйқўжЈҖжҹҘжңүж— chippingпјҢйҡҗиЈӮгҖӮ

Q4

жңүиө„жәҗеҸҜд»ҘжөӢйҮҸICеҺҡеәҰеҗ—пјҹtoleranceиҰҒжұӮеңЁВұ0.15umеҶ…

A4

иҝҷдёӘжңәеҸ°еҸҜд»Ҙж»Ўи¶ігҖӮ

Q5

зҺ°еңЁйҒҮеҲ°дёӨз§Қжғ…еҶөпјҢ

1.йҳҲеҖјз”өеҺӢеўһеҠ пјҢRdsonеўһеҠ пјҢеә”иҜҘжҳҜй—ЁжһҒжІҹйҒ“з”өйҳ»еўһеҠ дәҶгҖӮдҪҶжҳҜжҲ‘дёҚзҹҘйҒ“з”Ёд»Җд№ҲжүӢж®өеҲҶжһҗжІҹйҒ“з”өйҳ»еўһеҠ зҡ„еҺҹеӣ

2.иҠҜзүҮйҳҲеҖјз”өеҺӢйҷҚдҪҺпјҢдјҙйҡҸDSжјҸз”өжөҒе’ҢиҖҗеҺӢеӨұж•Ҳ

A5

е»әи®®е…Ҳе’ҢFoundry з»ҹи®ЎдёҖдёӢ WAT зҡ„жөӢйҮҸж•°жҚ®пјҢзңӢзңӢжңүжІЎжңүд»Җд№ҲејӮеёёпјҢеҲҶжһҗWATе’ҢMPж•°жҚ®еҲҶеёғпјҢзңӢзңӢжҳҜеҗҰжҳҜе·ҘиүәеҒҸе·®гҖӮ

Q6

жөӢзғӯйҳ»еҸӘжңүзғӯд»ҝзңҹиҝҷдёҖз§Қж–№ејҸеҗ—пјҹжңүжІЎжңүжҺЁиҚҗе“Ә家иғҪжөӢиҝҷдёӘзҡ„пјҹ

A6

зғӯйҳ»еҸҜд»ҘзӣҙжҺҘжөӢпјҢAQG324жңүзғӯйҳ»жөӢиҜ•ж–№жі•д»Ӣз»ҚгҖӮеҺҹзҗҶе°ұжҳҜе°Ҹз”өжөҒдёӢпјҢе…ғеҷЁд»¶еҺӢйҷҚе’ҢRTжҲҗзәҝжҖ§е…ізі»гҖӮ

第дёҖжӯҘпјҢе…Ҳе°Ҹз”өжөҒе’ҢдёҚеҗҢе®Өжё©ж Үе®ҡзәҝжҖ§Kзі»ж•°гҖӮ

第дәҢжӯҘпјҢз»ҷеӨ§з”өжөҒеҠ зғӯиҠҜзүҮпјҢ然еҗҺж’ӨеҺ»еӨ§з”өжөҒпјҢз»ҷе°Ҹз”өжөҒжөӢиҜ•еҺӢйҷҚпјҢеҸ‘иҪ¬жҚўжҲҗTvjmaxпјҢйҷҚжё©зЁіе®ҡеҗҺпјҢеҶҚиҪ¬жҚўжҲҗTvjminпјҢиҫ“е…ҘеҠҹзҺҮе·ІзҹҘпјҢе°ұиғҪеҫ—еҲ°RthдәҶ

Q7

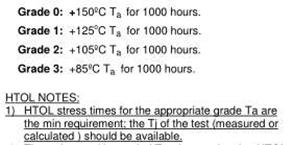

AECQзҡ„HTOLжөӢиҜ•пјҢжҳҜжҢүgradeзӯүзә§е®үжҺ’иҖҒеҢ–еҜ№еә”зҡ„зҺҜеўғжё©еәҰпјҲзӯүдәҺgradeжё©еәҰпјүпјҢиҝҳжҳҜжҢүз»“жё©жқҘе®үжҺ’иҖҒеҢ–зҺҜеўғжё©еәҰпјҲжҜ”еҰӮи°ғж•ҙTjеҲ°125пјүгҖӮеҘҪеғҸ2з§ҚиҜҙжі•йғҪжңүзңӢеҲ°иҝҮгҖӮ

A7

AECQзҡ„HTOLжөӢиҜ•жҳҜжҢүз…§зҺҜеўғжё©еәҰеҒҡзҡ„пјҢдёҚжҳҜжҢүз…§з»“жё©гҖӮ

Q8

еҰӮжһңжҢүз…§Gradeзӯүзә§зӣҙжҺҘжҚўжҲҗиҖҒеҢ–зҺҜеўғжё©еәҰпјҢеҜ№дәҺgrade3пјҢgrade2иҰҒжұӮе°ұжҜ”иҫғдҪҺдәҶгҖӮ1000hжҖҺд№ҲдҝқиҜҒзӣёеә”зҡ„й•ҝеҜҝе‘Ҫпјҹ

A8

дёҖиҲ¬йғҪжҳҜж №жҚ®жүҖйңҖзӯүзә§жқҘеҖ’жҺЁжүҖйңҖе®һйӘҢTjгҖӮеҸҰдёҖж–№йқўпјҢе®ўжҲ·з«Ҝжӣҙе…іеҝғзҡ„д№ҹжҳҜTjпјҢеҗҢж ·зҡ„иҠҜзүҮпјҢеҗҢж ·зҡ„зҺҜеўғжё©еәҰз”ЁдёҚеҗҢзҡ„жЁЎз»„ж•Јзғӯж–№жЎҲпјҢTjеҸҜиғҪйқһеёёеӨ§пјҢиҖҢжӯЈзңҹеҪұе“Қlifetimeзҡ„жҒ°жҒ°жҳҜTjгҖӮ

Q9

иҠҜзүҮзҡ„зғҳзғӨжңүжІЎжңүjedecзҡ„ж ҮеҮҶпјҹ

A9

жңүгҖӮиҜ·еҸӮиҖғJ-STD-33гҖӮ

Q10

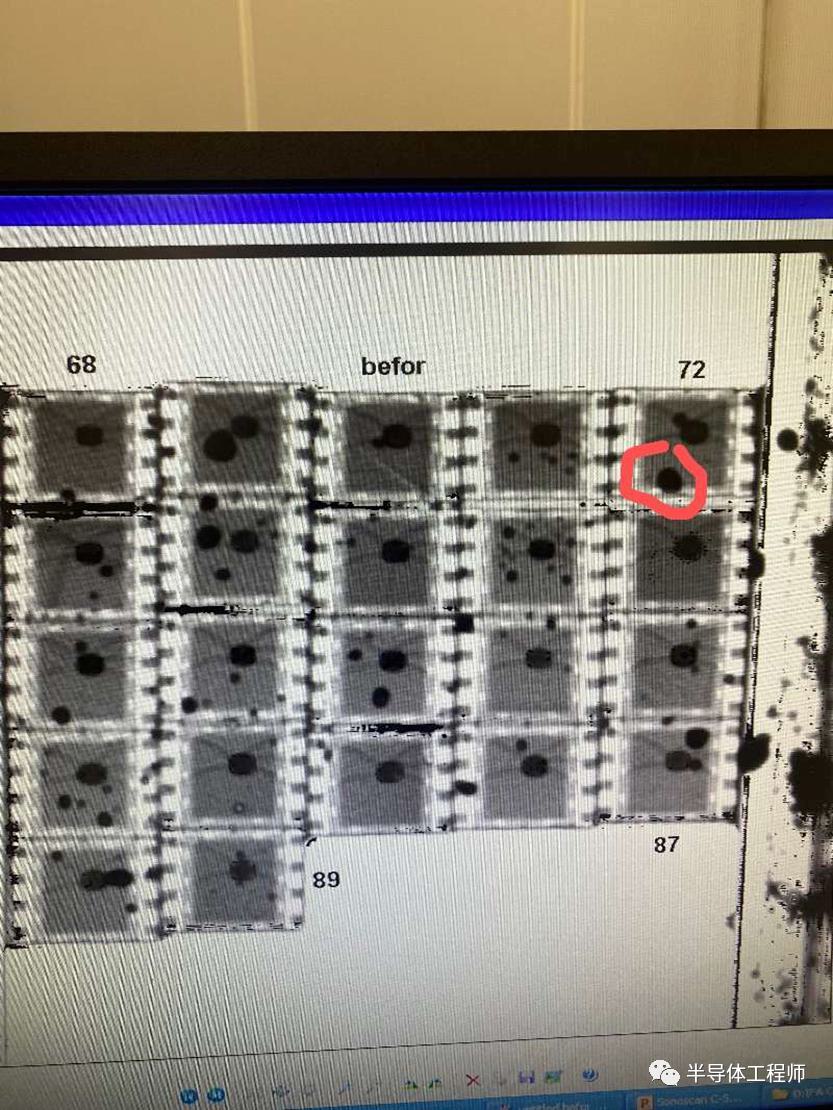

дёҠеӣҫжҳҜжҹҗж¬ҫиҠҜзүҮзҡ„t-scanеӣҫпјҢиҜ·ж•ҷдёӢеҗ„дҪҚпјҢзұ»дјјзәўеңҲжүҖзӨәдёӯжҳҜд»Җд№Ҳжғ…еҶөе•Ҡпјҹ

A10

еҸҜиғҪжҳҜж°”жіЎжІЎжңүжё…зҗҶе№ІеҮҖгҖӮ

Q11

её®еҝҷзңӢдёӢDFNе°ҒиЈ…дә§е“ҒжөӢиҜ•Vdd,е‘Ҳй«ҳйҳ»жҖҒгҖӮdecapиЎЁйқўзңӢз„ҠзҗғеҪўиІҢжӯЈеёёпјҢpadзңӢиө·жқҘд№ҹиў«и…җиҡҖдәҶпјҢдҪҶжҳҜеҲҶжһҗжңәжһ„еҲӨе®ҡзәҝжІЎжңүе…Ёи„ұпјҢдҪҶжҳҜзҝҳиө·жқҘдәҶгҖӮиҝҷз§Қжғ…еҶөдёҖиҲ¬дјҡжҳҜд»Җд№ҲеҺҹеӣ йҖ жҲҗпјҹеҰӮдҪ•зЎ®и®Өпјҹ

A11

е»әи®®йҖҒеӯЈдё°еҒҡиҜҰз»ҶеҲҶжһҗгҖӮеҸҜд»Ҙе…Ҳз ”зЈЁеҲ°з„Ҡзҗғи¶іеӨҹи–„пјҢ然еҗҺеҒҡFIBзңӢжҳҜеҗҰжңүзәҝзҙўпјҢеҸҜд»ҘиҝӣдёҖжӯҘеҒҡжҲҗд»ҪеҲҶжһҗпјҢдҪҶеҚ•йў—еӨұж•Ҳж ·е“ҒеҒҡеҲҶжһҗзҡ„ж—¶еҖҷжңҖеҘҪйҖүжӢ©зӣёеҜ№дҝқе®Ҳзҡ„ж–№жЎҲгҖӮ

Q12

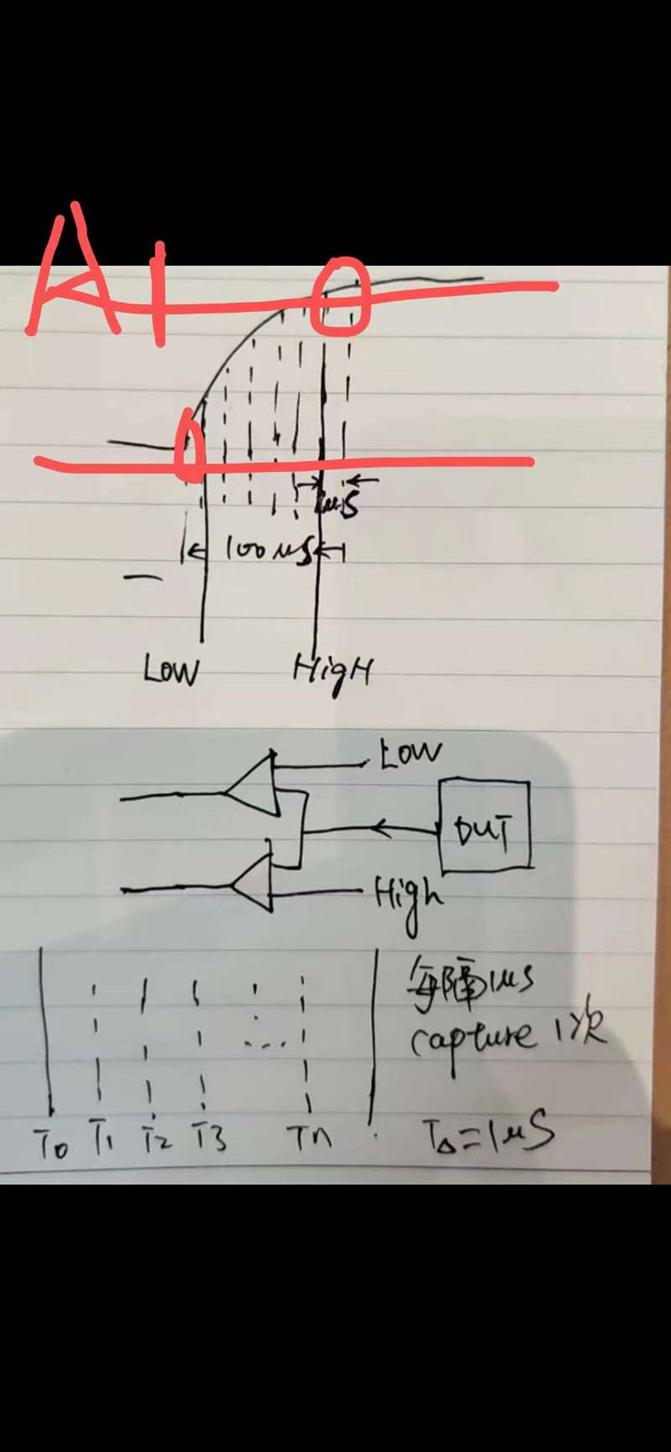

Need uS resolution to measure startup timing measure using digital I/O and DCиҝҷдёӘз”ЁATEе’ӢжөӢд№Ҳпјҹ

A12

еҸӘйңҖиҰҒA1 иҫҫеҲ°дҪ йңҖиҰҒзҡ„еҖј.д№ҹе°ұstart up дәҶ.иҝҷж—¶еҖҷpattern з”ЁеӨҡе°‘ж—¶й—ҙеҸҜд»ҘиҜ»еҸ–пјҢжҲ‘жөӢзҡ„жҳҜе°„йў‘иҠҜзүҮ.Y иҪҙжҳҜеҠҹзҺҮ.дҪ 们Y иҪҙйңҖиҰҒеҸӮиҖғдҪ 们зҡ„дә§е“ҒпјҢеҰӮжһңжҳҜMCUдә§е“ҒпјҢATEжңүTMU зҡ„еҚ•е…ғпјҢзӣҙжҺҘи®ҫе®ҡйҮҸжөӢж—¶й—ҙжҜ”patternеҮҶзЎ®еҫҲеӨҡгҖӮ

Q13

жҺҘд»ҘдёҠй—®йўҳпјҢTMUжҲ–иҖ…patternзҡ„ж–№ејҸеә”иҜҘйғҪжҳҜеҲ©з”ЁPEиҠҜзүҮйҮҢйқўзҡ„comparatorд№Ҳпјҹ

A13

еҜ№зҡ„пјҢи§ҰеҸ‘д№ҹжҳҜVOLпјҢVOH2дёӘз”өе№іпјҢеҸӘжҳҜж—¶й—ҙзҡ„еҸӮиҖғе…ғе’ҢеӯҳеӮЁзҡ„ж–№ејҸдёҚдёҖж ·пјҢTMUд»Ҙи§ҰеҸ‘жқЎд»¶и®°еҪ•пјҢж—¶й—ҙеҸҜд»ҘжҜ”иҫғй•ҝпјҢдёҖиҲ¬жңү24bitзҡ„и®Ўж•°еҷЁпјҢеҰӮжһңдҪҝз”ЁpatternжҠ“еҸ–пјҢеңЁжҠ“еҸ–зҡ„ејҖзӘ—е‘ЁжңҹжІЎжңүеҸ‘з”ҹдёҠеҚҮпјҢеҸҜиғҪдјҡй”ҷиҝҮпјҢеҸҰеӨ–пјҢдҪҝз”Ёpattern жҠ“еҸ–дёҖж®өжіўеҪўпјҢдёӯй—ҙзҡ„ж—¶й—ҙйңҖиҰҒзј–зЁӢиҝӣиЎҢеҲҶжһҗжүҚиғҪиҪ¬жҚўеҮәжқҘгҖӮ

Q14

datasheetеҸҳжӣҙпјҢеӨ§е®¶йғҪдјҡеҸ‘PCNйҖҡзҹҘе®ўжҲ·еҗ—пјҹиҝҳжҳҜе°ұжҳҜе®ҳзҪ‘ж”ҫдёҖдёӢжңҖж–°зүҲжң¬е°ұз®—дәҶпјҹеҰӮжһңж”№дәҶac parametersдёӢйҷҗпјҢиҝҷз§ҚиҰҒйҖҡзҹҘеҗ—пјҹиҝҳжҳҜиҮӘе·ұеҲӨж–ӯеҜ№е®ўжҲ·жІЎеҪұе“Қе°ұдёҚз”ЁйҖҡзҹҘдәҶпјҹ

A14

еҸӘиҰҒdatasheetеҸҳжӣҙпјҢйғҪйңҖиҰҒйҖҡзҹҘе®ўжҲ·гҖӮ

жқҘжәҗпјҡдёҠжө·еӯЈдё°з”өеӯҗ