扇出晶圆级封装 ( FO WLP:Fan-out wafer-level packaging ) 是行业从晶体管缩放向系统缩放和集成转变的关键推动力。该设计通过重新分布层(redistribution layer)而不是基板扇出芯片互连。与倒装芯片球栅阵列 (FCBGA:flip-chip ball grid array) 或引线键合相比,这种设计可产生更低的热阻、更纤薄的封装,并可能降低成本。

然而,如果希望通过消除基板来降低成本,那么现实情况是,缺乏基板会导致芯片移位和翘曲,从而降低成本。所以工程师正在通过改进光刻、取放和成型操作(热压或激光键合)来解决die移位(die shift)问题。

“对于一两个die来说,这是一项很棒的技术,” Cadence Design Systems的 IC 封装产品管理总监 John Park 说。“但一旦你获得了六个或更多chiplets,限制因素就是die shift。显然,你拥有的die越多,每个die就会稍微偏移一到两个度数,然后你把六个放在一起,就再也没有任何连接了。”

然而,诸如封装基板的交货时间长等问题正在加速 FOWLP 的采用。“移动和高性能计算/网络是我们看到的一些领域,除了低引脚数、电源管理扇出晶圆级结构之外,传统上它是主要的 FOLWP 应用,”ASE的工程和技术营销高级总监 Mark Gerber 说。

总的来说,FOWLP 作为一种解决方案正在推进。在 Apple 的 M1 Ultra 芯片中,台积电的 InFO 扇出工艺被选择用于其最新的应用处理器(见图 1),而不是基于基板的工艺。这是更广泛趋势的一部分。根据 Yole Developpement 的数据,扇出封装市场预计将以 15% 的复合年增长率增长,到 2026 年达到34亿美元。Yole 分析师预计,到 2025 年,93% 的产能将用于晶圆级封装,7% 将在面板级进行加工。

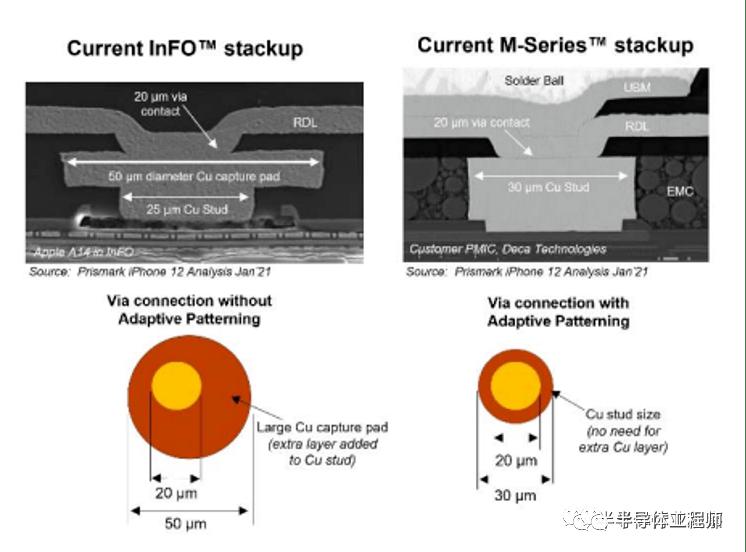

图 1:在 TSMC 的 InFO 和 Deca 的 M 系列中连接到 via 的最先进的 RDL。资料来源:es目前量产的其他产品包括射频设备、电源管理 IC (PMIC)、基带处理器和高端服务器芯片。5G 应进一步推动扇出封装的采用,因为更短的互连和更低的电感可带来卓越的射频和毫米波性能。

图 1:在 TSMC 的 InFO 和 Deca 的 M 系列中连接到 via 的最先进的 RDL。资料来源:es目前量产的其他产品包括射频设备、电源管理 IC (PMIC)、基带处理器和高端服务器芯片。5G 应进一步推动扇出封装的采用,因为更短的互连和更低的电感可带来卓越的射频和毫米波性能。“对于毫米波天线和毫米波封装的 FOWLP 进行了很多讨论和建模,” Onto Innovation先进封装战略营销总监 Monita Pau 博士说。“这使得介电材料成为一个非常重要的元素。您必须具有非常好的机械性能和非常低的损耗介电性能,因为您将毫米波天线与扇出封装集成在一起。此外,需要低铜 RDL 粗糙度和适应形貌的光刻技术来实现再分布层的良好 CD 均匀性,这对于实现高增益和低损耗传输至关重要。”

扇出技术的溯源

扇出有着悠久的历史。这种封装方法于 2007 年首次推出,当时英飞凌设计了其嵌入式晶圆级 BGA (eWLB)。但第一波采用是在 2016 年台积电在 iPhone 7 中使用 InFO 之后。TechSearch International总裁 Jan Vardaman说。

虽然自 iPhone 7 以来手机一直是典型的用例,但 FOWLP 设计也可以扩展到超级计算机等设备。较新的应用包括网络交换产品、手机和智能手表的 PMIC 以及 AI 芯片。

对于高端应用中的组装,OSAT 和代工厂正在将扇出封装与基板耦合在一起。“以前人们常说不用基板,直接贴在板子上就行了,现在因为高密度要求,需要基板才能贴在PCB板上, ”Pau 说。

今天的 FOWLP 设计还支持更灵活的设计。Gerber 说:“我们的基板桥上扇出芯片 (FOCoS-B) 支柱可以在重分布层之间集成一个或多个裸片,在非常接近有源硅电路的位置集成深沟槽电容器、稳压器等。这将系统级损失降至最低,从而获得更高的性能。”

工艺

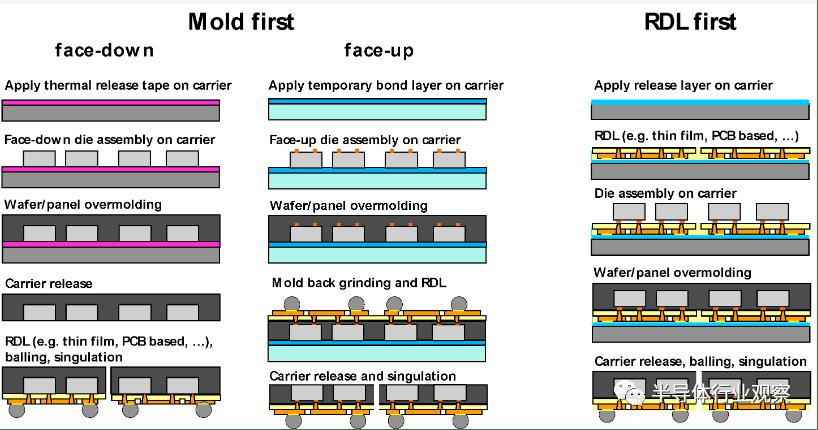

扇出工艺流程分为两类,die first(也称为mold first))和 RDL first(见图 2)。Dies也可以面朝上或面朝下放置在载体晶圆或面板上。

图 2:die first配置和 RDL first的工艺流程。资料来源:Fraunhofer IZM在die first,首先将热剥离胶带(thermal release tape)贴在载体晶圆(carrier wafer,)上,然后拾取KGD( known good die)并将其放置在载体上。接下来,overmolding 之后是carrier release, RDL formation, solder bumping,,然后是singulation。首先在 RDL 中,首先再次沉积释放层,然后是 RDL、KGD 定位,然后是overmold, carrier release, solder ball deposition和singulation。

图 2:die first配置和 RDL first的工艺流程。资料来源:Fraunhofer IZM在die first,首先将热剥离胶带(thermal release tape)贴在载体晶圆(carrier wafer,)上,然后拾取KGD( known good die)并将其放置在载体上。接下来,overmolding 之后是carrier release, RDL formation, solder bumping,,然后是singulation。首先在 RDL 中,首先再次沉积释放层,然后是 RDL、KGD 定位,然后是overmold, carrier release, solder ball deposition和singulation。虽然扇出从经典组装技术开始,但它也需要非传统工艺。Promex工程副总裁 Chip Greely 说:“它添加了您通常看不到的东西,例如在晶圆骨架上(wafer skeleton )压缩成型以填充区域,然后研磨塑料材料模具化合物(mold compound),而不是背面研磨晶圆。”“然后你在上面沉积一个铜重新分配层,这让你的三个 actors远离一些装配厂所接受的范围。通常,当您对硅或任何这些晶体材料进行背面研磨时,它们往往会很容易成粒并被洗掉。Mold compound往往会粘稠并起球,因此您的砂轮会充满塑料,需要使用秘方将其去除。”尽管如此,他说,只要有足够的设备,规模经济就会发挥作用。

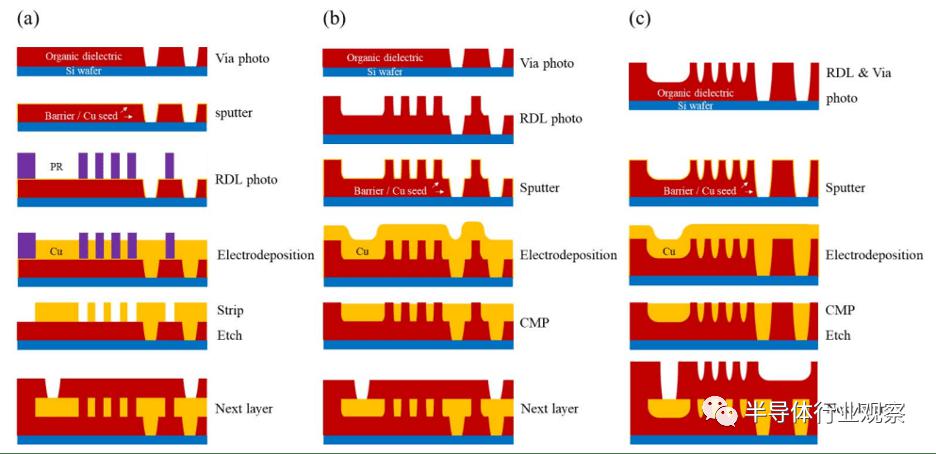

相对于扇入WLP,扇出如此受欢迎的原因是它可以容纳更多的 I/O 连接。当今最先进的扇出封装具有多达五层的 RDL(见图 3),线和间距低至 2µm(金属迹线的宽度和间距)。扩展到微米互连范围意味着 RDL 工艺开始看起来更像是片上双镶嵌集成(dual damascene integration)。

图 3:再分布层由聚酰亚胺电介质中的铜迹线组成。资料来源:Lam Research例如,Amkor最近为其 S-SWIFT 扇出技术展示了一种嵌入式迹线 RDL (ETR),该技术可以扩展到小于 2/1 的线/空间和过孔。新工艺将 ASIC 与两个高带宽内存 (HBM) 芯片集成在一起。创新包括through-mold的铜柱、高密度 RDL、均匀的介电涂层、优化的镀铜、CMP 和湿法蚀刻,以实现比POR(process of record) 更简单、更可扩展的工艺。

图 3:再分布层由聚酰亚胺电介质中的铜迹线组成。资料来源:Lam Research例如,Amkor最近为其 S-SWIFT 扇出技术展示了一种嵌入式迹线 RDL (ETR),该技术可以扩展到小于 2/1 的线/空间和过孔。新工艺将 ASIC 与两个高带宽内存 (HBM) 芯片集成在一起。创新包括through-mold的铜柱、高密度 RDL、均匀的介电涂层、优化的镀铜、CMP 和湿法蚀刻,以实现比POR(process of record) 更简单、更可扩展的工艺。Amkor 副总裁 SangHyun Jin 和他的团队改进了 POR,这是一种半加成工艺(见图 4a)。对工艺变化进行了探索,以克服高 AR 迹线塌陷、通孔中的光刻胶残留和侧壁蚀刻问题的可能性。

Amkor 团队首先开发了一种双镶嵌工艺(图 4b),该工艺将铜迹线嵌入聚合物层中。这种变化提高了 RDL 与衬底的粘附性,并且通过在沟槽的三个侧面沉积阻挡层,提高了可靠性。该团队指出,通孔和 RDL 是通过使用有机电介质旋涂的两道光刻工艺分别形成的。固化后,对种子层和铜进行电镀,然后进行 CMP 和湿法蚀刻。

最终工艺(图 4c)将通孔和 RDL 图案组合到一个掩模中,将工艺步骤减少了 40%。此更改还消除了通孔和捕获焊盘之间的错位。将三步 CMP 工艺改为单 CMP,然后进行湿法蚀刻。CMP 确保每个 RDL 的轮廓更平坦,并且在四层 RDL 上制造具有 1μm 间距的 2μm 线,可扩展至六层。组装后,工程师对异构设备进行了可靠性测试。

图 4:将 RDL 半加成工艺 (a) 修改为双镶嵌 (b),然后简化镶嵌 (c) 工艺,该工艺可扩展到 2/1μm 线/空间迹线。资料来源:安靠同样在 ECTC,ASE 工程总监 Lihong Cao 和她的团队展示了如何使用扇出 RDL 来降低多层有机中介层 (ABF) 基板上 ASIC 的复杂性和成本。ASE 能够将 14 层基板转换为具有 2 个 RDL 的 8 层。第二个测试设备显示使用 1 个 RDL 将 10 层基板减少到 4 层。这种变化将降低与日益复杂的基板相关的成本和产量损失。

图 4:将 RDL 半加成工艺 (a) 修改为双镶嵌 (b),然后简化镶嵌 (c) 工艺,该工艺可扩展到 2/1μm 线/空间迹线。资料来源:安靠同样在 ECTC,ASE 工程总监 Lihong Cao 和她的团队展示了如何使用扇出 RDL 来降低多层有机中介层 (ABF) 基板上 ASIC 的复杂性和成本。ASE 能够将 14 层基板转换为具有 2 个 RDL 的 8 层。第二个测试设备显示使用 1 个 RDL 将 10 层基板减少到 4 层。这种变化将降低与日益复杂的基板相关的成本和产量损失。Die shift

die被拾取并放置在载体晶圆上后的任何时候都可能发生Die shift,但最大的风险是在molding compound processing中,这会影响良率。

通过使用激光辅助键合或热压键合代替传统的mass flow,可以减少die shift 。另一种方法是自适应模式,由Deca创建并内置在 Cadence 的 EDA 工具中。它很快将可用于Synopsys和Siemens EDA工具。在自适应图案化(见图 5)中,工艺工程师在光刻工具上精确测量芯片和互连位置,然后将沉积的 RDL 图案调整到这些位置。

图 5:自适应图案将过孔和 RDL 触点与芯片的实际位置对齐。资料来源:decaDeca Technologies首席执行官 Tim Olson 表示:“在设计过程中,您可以确定哪种 AP 技术最能帮助您扩展到更高的密度或调整制造工艺能力以实现 100% 或非常接近的良率。”“因此,您在设计过程中会做出关于将使用哪个制造工厂的决定。一旦您将设计发布到制造阶段,我们在台湾、菲律宾和韩国的被许可方的图案化引擎就会拥有服务器,在每个晶圆或每个面板上,我们都会进行高速光学扫描以定位 I/O。该引擎在其中一个 EDA 系统上获取设计指令,然后按 RDL 层执行,进行对齐或优化。在某些情况下,它会重新绘制以适应变化。” 最后,将 GDSII 文件转换为数字位图,并由兼容的无掩模光刻工具用于打印对齐的连接。

图 5:自适应图案将过孔和 RDL 触点与芯片的实际位置对齐。资料来源:decaDeca Technologies首席执行官 Tim Olson 表示:“在设计过程中,您可以确定哪种 AP 技术最能帮助您扩展到更高的密度或调整制造工艺能力以实现 100% 或非常接近的良率。”“因此,您在设计过程中会做出关于将使用哪个制造工厂的决定。一旦您将设计发布到制造阶段,我们在台湾、菲律宾和韩国的被许可方的图案化引擎就会拥有服务器,在每个晶圆或每个面板上,我们都会进行高速光学扫描以定位 I/O。该引擎在其中一个 EDA 系统上获取设计指令,然后按 RDL 层执行,进行对齐或优化。在某些情况下,它会重新绘制以适应变化。” 最后,将 GDSII 文件转换为数字位图,并由兼容的无掩模光刻工具用于打印对齐的连接。“我们有一种新方法可以消除捕获垫,”Olson指出。“我们发明了捕获垫来吸收重叠公差。通过自适应图案化,我们可以在不使用捕获垫的情况下实现突破性密度。” 他补充说,拾取和放置的规格只需要 15µm,而在没有自适应图案的情况下需要更高的精度,这会显着降低工具吞吐量。

正如Brewer Science 解释的那样,还可以通过改进粘合材料的选择来解决die shift问题:“为了使粘合材料在die放置过程中保持最小的垂直变形和在over-molding过程中保持最小的die shif,它们必须具有高熔体粘度和高热稳定性。由于载体和基板材料的热膨胀系数 (CTE) 之间的不匹配,这一点尤为重要。键合材料还必须以最小化堆叠晶圆中的应力效应的方式进行定制,其中可能发生翘曲,从而导致对准和处理问题。它们应该对基材有足够的附着力,才能承受这样的压力。”

应力和翘曲老化硅、聚酰亚胺(在 RDL 中)和环氧模塑料之间的 CTE 不匹配会产生翘曲问题。翘曲导致产量损失。

“翘曲绝对是个问题。这就是为什么很多人正在转向压缩成型和底部浇口、压缩成型而不是顶部系统,”Greely 说。

另一种减少应力和翘曲的方法是选择具有较低固化温度的更好的介电材料。

走向面板级?扇出面板级封装 ( FO PLP ) 是晶圆级扇出的扩展,它利用了SEMI标准尺寸 510 x 515 毫米或 600 x 600 毫米的更大基板尺寸。三星的 Galaxy 手表 2018 年 FOPLP 很早就引起了轰动。Nepes去年在菲律宾推出了第一个扇出面板级封装操作,使用 600 x 600um 面板。三星、Powertech、Unimicron和ASE已经或即将拥有量产的 FOPLP。

尽管这些公司似乎正在向前发展,但 FOPLP 基本上处于搁置状态,直到产量表明需要从晶圆载体大规模转换为面板级处理。目前尚不清楚这种情况何时会改变。“如果他们说五年是一个机会之窗,我至少会增加三倍,”Greely说。“面板化是个好主意,但当你深入细节时会遇到挑战。这就像告诉人们我们将拥有一个标准化的chiplet。”

设计虽然面板可能还在未来,但基本的 FOWLP 布局已被广泛接受,以至于自动化设计工具已经很成熟。据 Park 称,Cadence 已与知名代工厂商认证设计流程,并将在即将举行的 LIP 上宣布进一步的发展。

然而,Park 警告说,包装与层压板是不同的世界。例如,封装具有独特类型的设计规则,例如“zigzag insertion”,即需要在侧线中中断以提高良率。

“传统的封装工具输出 Gerber 文件格式 (.grb),这是用于层压基板而非晶圆的制造格式,”Park 说。“当你制造层压板时,没有像 DRC 和 LBF 那样的正式签核流程,就像制造晶圆时那样。”

为了解决这个问题,Cadence 创建了一个扩展,将 IC 验证工具与封装物理设计工具连接起来。“如果有人是 IC 世界的新手,他们可以在 GUI 中选择他们想要检查的规则,该工具将执行 LBS 和 DRC。然后,该运行的任何结果都将在布局工具中呈现给用户,”Park 说。

无论工程师以前的经验如何,还有其他问题可以挑战工程师。“对超高密度 RDL 的要求,例如在 TSMC 的 inFO 中发现的,比封装设计人员过去必须处理的任何事情都要严格得多,”他说。设计工具现在正在考虑金属平衡,例如空化焊盘和通孔以及脱气铜填充区域等问题。

最后,还有电导率验证,当涉及多个小芯片时,这可能会非常复杂。“它可能会在生产的最后阶段出现,”Park 说,“但你必须尽早考虑,因为驱动 LVS 的网表必须在设计的早期阶段建立。”

结论业界正在寻找多种方法来使用扇出封装来简化封装并简化流程。“我们让客户用 5 层 RDL 替换 12 层基板,同时机身尺寸缩小了 20%,”Deca 的 Olson 说。“扇出目前比基板解决方案更昂贵,但如果您能够减少层数,它在成本上非常具有竞争力。”

Vardaman 认为未来需要芯片优先和芯片后两种方案。“一切都是为了为你想做的事情选择正确的封装和正确的结构。”

来源:集成电路前沿

欢迎各公众号,媒体转载

投稿/推广/合作/入群/赞助/转发 请加微信13488683602