Q1

InGaAsзҡ„иҠҜзүҮпјҢжңүжІЎжңүеҠһжі•д»ҺиҠҜзүҮзүҲеӣҫжҲ–иҖ…еҖҹеҠ©жҹҗдәӣFAжүӢж®өзңӢеҮәжқҘжҳҜphemtжҲ–hbtе·Ҙиүәпјҹ

A1

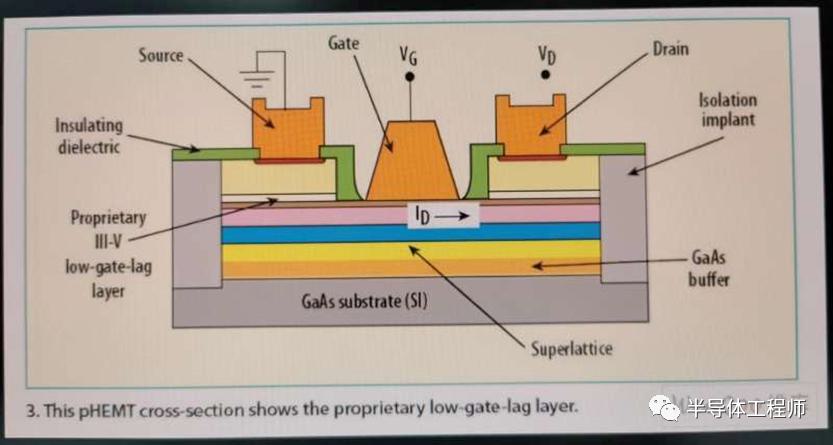

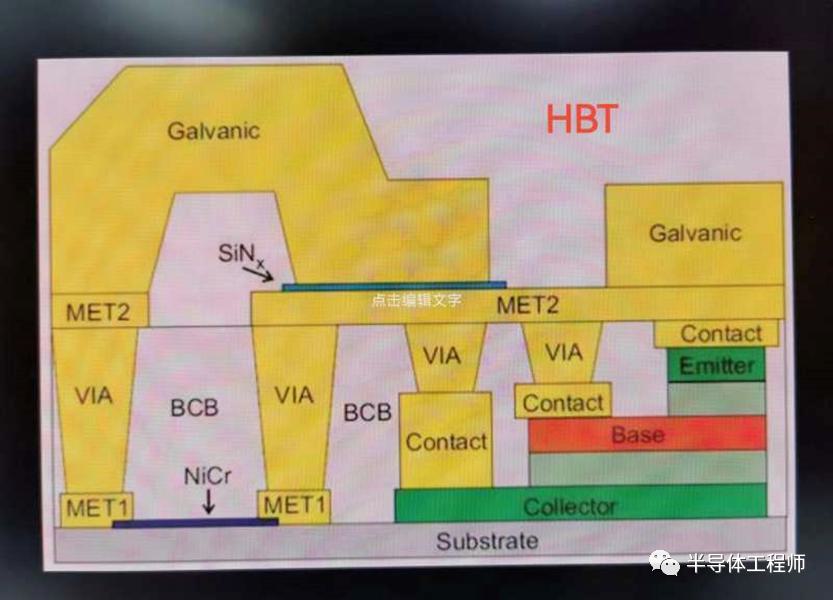

зҪ‘дёҠжүҫзҡ„зӨәж„ҸеӣҫеҸҜд»ҘеҸӮиҖғдёҖдёӢгҖӮе…¶е®һзңӢзүҲеӣҫжҲ–иҖ…е®һйҷ…dieзҡ„з…§зүҮд№ҹеә”иҜҘжҜ”иҫғе®№жҳ“еҲҶиҫЁгҖӮжІЎжңүзӨәж„ҸеӣҫдёҚжҳҜеҫҲеҘҪжҸҸиҝ°гҖӮиҝҳжңүе°ұжҳҜйҖҡиҝҮdieзҡ„еҠҹиғҪпјҢPAжҳҜHBTзҡ„пјҢLNAжҳҜPHEMTзҡ„пјҢжҚ®жҲ‘зҡ„дәҶи§ЈдёҖиҲ¬жҳҜиҝҷж ·гҖӮйӮЈз§ҚеӨ§йқўз§Ҝзҡ„PHEMTзҡ„з®Ўеӯҗз»„жҲҗзҡ„зәҜ swtich dieи¶ҠжқҘи¶Ҡе°‘и§ҒпјҢжӣҙеӨҡең°иў«SOIзҡ„swtichеҸ–д»ЈгҖӮ

Q2

иҜ·й—®дёӢжЈҖжҹҘBGAзҡ„з„ҠжҺҘпјҢеҒҡеҲҮзүҮзңӢеҲ°зҡ„ж•ҲжһңжҳҜдёҚжҳҜжҜ”3d-RayжӣҙеҠ зӣҙи§ӮпјҹжЈҖжҹҘиҠҜзүҮз„ҠжҺҘзҡ„иҙЁйҮҸпјҢдҪҝз”ЁзәўеўЁж°ҙпјҢ3DxayпјҢжҲ–иҖ…еҒҡеҲҮзүҮеҲҶжһҗпјҢеңЁжЈҖжҹҘиҠҜзүҮз„ҠжҺҘдёҠеҲҶеҲ«жңүд»Җд№ҲдјҳеҠҝе’ҢеҠЈеҠҝпјҹ

A2

зәўеўЁж°ҙеҸҜд»ҘзңӢеҲ°е®һдҫӢзҡ„з„ҠжҺҘйқўпјҢе’Ң3Dзұ»дјјпјҢжғіиҰҒзңӢз»ҶиҠӮжңҖеҘҪз»“еҗҲзқҖ3DеҶіе®ҡеҰӮдҪ•еҲҮзүҮпјҢеҲҮзүҮеҸҜд»ҘзңӢеҲ°жӣҙеӨҡз»ҶиҠӮпјҢжҜ”еҰӮSNWжҳҜеӣ дёәејӮзү©иҝҳжҳҜеӣ дёәеҹәжқҝжң¬иә«зҡ„зјәйҷ·зӯүгҖӮжҖ»д№ӢпјҢеүҚдёӨдёӘеҲҶжһҗзңӢдёҚеҲ°з»ҶиҠӮгҖӮ

Q3

TSMC 130nm wafer зҡ„еҺҡеәҰжҳҜеӨҡе°‘е‘ўпјҹ

A3

waferеҮәжҷ¶еңҶеҺӮдёҖиҲ¬йғҪжҳҜ750umе·ҰеҸігҖӮдҪҶжҳҜеҲ°дәҶе°ҒиЈ…еҺӮйғҪиҰҒиҝӣиЎҢеҮҸи–„пјҢиҮідәҺеҮҸи–„еҲ°еӨҡе°‘еҺҡеәҰпјҢйӮЈиҰҒдҫқжҚ®е°ҒиЈ…еҪўејҸпјҢз”өжҖ§пјҢж•ЈзғӯзӯүйңҖжұӮиҖҢе®ҡгҖӮ

Q4

CSPе°ҒиЈ…fan-outе·ҘиүәпјҢйғҪжҳҜеңЁзЈЁзүҮеҗҺе°ұиҙҙдёҠеҲ’зүҮиҶңдәҶеҗ—пјҢиҖҢдёҚжҳҜеғҸfan-inдёҖж ·пјҢеңЁжү“дёқеҚ°еҗҺжүҚиҙҙжҳҜеҗ—пјҹйӮЈиҝҷж ·дјҡеҜјиҮҙжү“еҚ°зҡ„ж—¶еҖҷиғҪйҮҸдёҚи¶іпјҢеӯ—дҪ“еҫҲз»ҶжҳҜеҗ—?

A4

FOжү“ж ҮжҳҜжү“еңЁеЎ‘е°Ғж–ҷдёҠзҡ„пјҢйҷӨйқһдҪ жҳҜBGжјҸSiгҖӮжңүBackside laminationпјҢйҖҸиҶңжү“ж ҮпјҢжӣҙжё…жҷ°дё”дёҚжҠўSiгҖӮ

Q5

AECQ101дёәд»Җд№ҲйҖүеҸ–ж ·жң¬жҳҜ77йў—dieеҗ—пјҹжҲ–иҖ…AQG324 ж ·жң¬йҖүеҸ–6дёӘswitchпјҹж ·жң¬йҖүеҸ–зҡ„дҫқжҚ®жҳҜд»Җд№Ҳпјҹ

A5

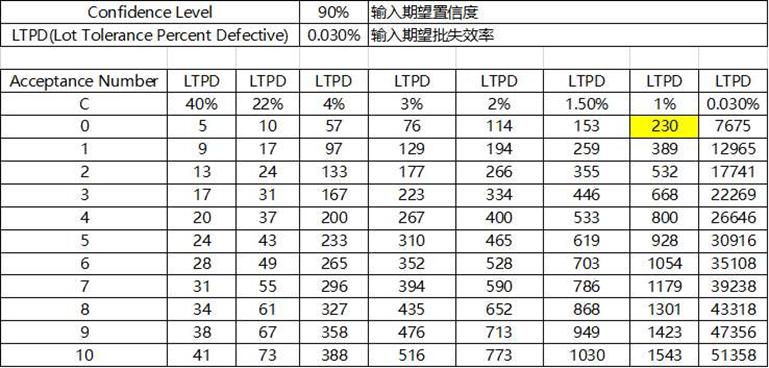

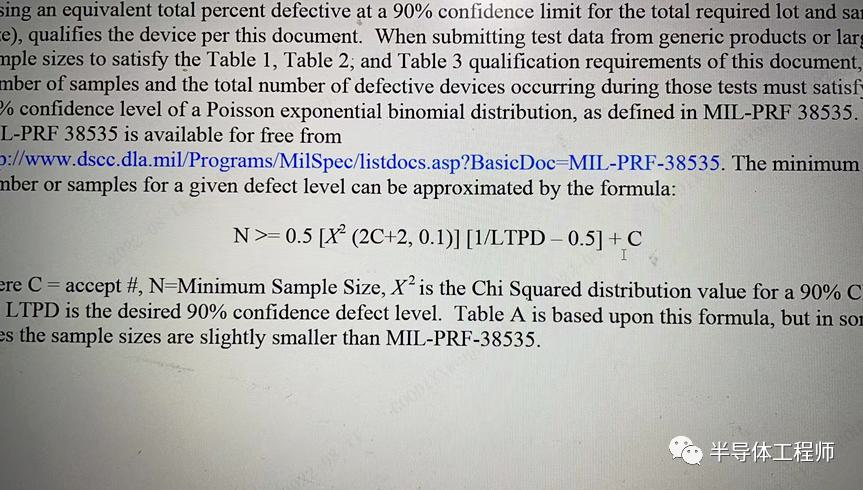

AECQжҳҜжҢүз…§LTPDжқҘжҠҪж ·зҡ„пјҢеҺҹжқҘжҳҜ0/231жҢүз…§LTPd1%жқҘеҸ–ж ·зҡ„гҖӮ

Q6

LTPDе’ҢзҪ®дҝЎеәҰд»ҘеҸҠж ·жң¬ж•°д№Ӣй—ҙжңүи®Ўз®—е…¬ејҸеҗ—пјҹ

A6

JEDEC47дёҠжңүиҝҷдёӘе…¬ејҸ

Q7

vtranжңүдәәз”ЁиҝҮжқҘиҪ¬еҗ‘йҮҸеҗ—пјҹ

A7

15е№ҙеүҚеӣҪеӨ–з”ЁиҝҮvtranпјҢж„ҹи§үеҫҲдёҖиҲ¬гҖӮеҗҺйқўжӣҙеӨҡдәәз”Ёwave wizardд№Ӣзұ»зҡ„гҖӮvtranжҳҜж–Үжң¬зҡ„пјҢиҰҒи°ғж•ҙиӣ®еӨҡзҡ„пјҢжІЎжі•зңӢжіўеҪўпјҢж„ҹи§үжҢәйә»зғҰгҖӮ

Q8

жӯЈеёёMSL3зҡ„еҷЁд»¶пјҢдёҚејҖе°Ғзҡ„жңүж•ҲжңҹжҳҜеӨҡд№…пјҹжңүиҝҷж–№йқўж–Ү件еҗ—пјҹ

A8

40в„ғе’Ң90%ж№ҝеәҰд»ҘдёӢеӯҳеӮЁпјҢ12дёӘжңҲгҖӮеҸӮиҖғJ-STD-033AгҖӮ

жқҘжәҗпјҡдёҠжө·еӯЈдё°з”өеӯҗ

ж¬ўиҝҺеҗ„е…¬дј—еҸ·пјҢеӘ’дҪ“иҪ¬иҪҪ

жҠ•зЁҝ/жҺЁе№ҝ/еҗҲдҪң/е…ҘзҫӨ/иөһеҠ©/иҪ¬еҸ‘ иҜ·еҠ еҫ®дҝЎ13488683602