Q1

иҜ·й—®QFP100и„ҡзҡ„е°ҒиЈ…дә§е“ҒпјҢдҪҺжё©жөӢиҜ•пјҢеҰӮдҪ•и§ЈеҶіж°ҙжұҪй—®йўҳпјҹеҰӮжһңеҗ№е№ІзҮҘж°”дҪ“пјҢйӮЈд№Ҳжё©еәҰе°ұдјҡйҷҚзҡ„еҫҲеҝ«пјҢжөӢдҪҺжё©ж•ҲжһңдјҡдёҚдјҡе·®еҫҲеӨҡпјҹ

A1

дҪ еҸҜд»Ҙзӣ‘жөӢдёӢдҪ зҡ„жөӢиҜ•зҺҜеўғзҡ„йңІзӮ№жё©еәҰпјҢдёҖиҲ¬йңІзӮ№жё©еәҰиҫҫеҲ°-60в„ғе°ұеҸҜд»ҘдәҶгҖӮ

Q2

иҜ·ж•ҷдёҖдёӢеҗ„дҪҚпјҢиҠҜзүҮFTжөӢиҜ•е®ҢжҲҗзңҹз©әеҢ…иЈ…д№ӢеүҚзғҳзғӨзҡ„жё©еәҰе’Ңж—¶й—ҙеҲҶеҲ«жҳҜеӨҡе°‘пјҹ

A2

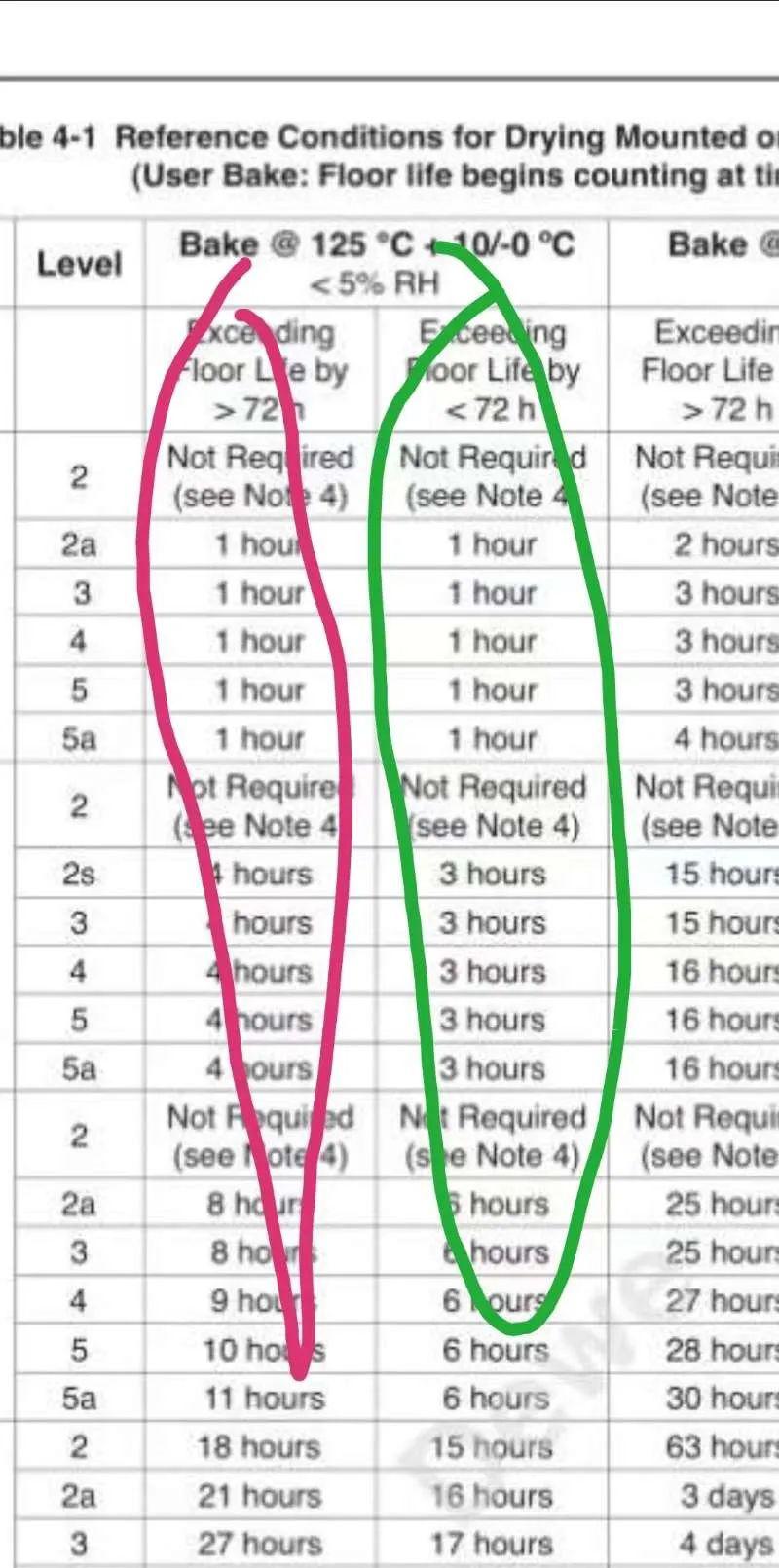

ж №жҚ®дҪ иҠҜзүҮзҡ„е°ҒиЈ…жқҗж–ҷд»ҘеҸҠеҺҡеәҰпјҢиҝҳжңүдёҚеҗҢзҡ„MSLж°ҙеҮҶпјҢBaking timeжҳҜдёҚеҗҢзҡ„гҖӮе…·дҪ“еҸӮиҖғJ-STD-033DпјҢFTд№ӢеҗҺпјҢжҜ”иҫғжҷ®йҒҚ125в„ғ x 8hпјҢеҶҚзңҹз©әеҢ…иЈ…гҖӮ

Q3

иҝҷдёӨеҲ—иЎЁзӨәд»Җд№Ҳж„ҸжҖқпјҹжұӮи§ЈйҮҠгҖӮ

A3

"floor life"иҪҰй—ҙеҜҝе‘Ҫ: д»Һйҡ”жҪ®иўӢйҮҢе°ҶеҷЁд»¶еҸ–еҮәеҗҺеңЁеёёжё©жӯЈеёёж№ҝеәҰжҺ§еҲ¶зҡ„иҪҰй—ҙзҺҜеўғе…Ғи®ёжҡҙйңІзҡ„жңҖй•ҝж—¶й—ҙпјҢжҲ–з»Ҹе№ІзҮҘзғҳзғӨеҲ°еӣһжөҒз„Ҡд№ӢеүҚжүҖе…Ғи®ёзҡ„ж—¶й—ҙгҖӮдҪ еңҲеҮәзҡ„дёӨеҲ—ж•°жҚ®жҳҜжҢҮиҠҜзүҮжҡҙйңІеңЁиҪҰй—ҙзҺҜеўғеҶ…и¶…иҝҮе’ҢжңӘи¶…иҝҮиҪҰй—ҙеҜҝе‘Ҫ72е°Ҹж—¶зҡ„еӨ„зҗҶж–№ејҸгҖӮеҰӮжһңеҷЁд»¶жҡҙйңІеңЁSMTиҪҰй—ҙзҺҜеўғзҡ„ж—¶й—ҙи¶…иҝҮиҪҰй—ҙеҜҝе‘ҪпјҢеҝ…йЎ»еҒҡbakingпјҢеҗҰеҲҷиҠҜзүҮеңЁеӣһжөҒз„Ҡзҡ„иҝҮзЁӢдёӯдјҡеҮәзҺ°popcorn damageзҺ°иұЎгҖӮж№ҝж°”иў«е°ҒиЈ…жқҗж–ҷ(дҫӢеҰӮпјҢmolding, substrate,underfillзӯү)еҗёж”¶еҗҺйӣҶиҒҡеңЁжқҗж–ҷз•ҢйқўеӨ„пјҢreflowй«ҳжё©дјҡдҪҝж№ҝж°”еҸҳдёәж°ҙи’ёж°”дҪ“з§ҜиҶЁиғҖеҜјиҮҙз•ҢйқўеҲҶеұӮdelamпјҢdie crackзӯүзјәйҷ·гҖӮ

Q4

иҜ·ж•ҷдёҖдёӢеҗ„дҪҚпјҢиҠҜзүҮеҝ«йҖҹORTд»Җд№Ҳж„ҸжҖқпјҢжҖҺд№ҲеҺ»и®ҫи®Ўе®һйӘҢпјҹдёҖиҲ¬еҒҡе“ӘдәӣйЎ№зӣ®пјҹжңүзӣёе…іж ҮеҮҶеҗ—пјҹ

A4

еҝ«йҖҹORT 44йў—дә§е“Ғйў„еӨ„зҗҶеҗҺпјҢTCT100cyc 22йў— ,UHAST 48h 22йў—пјҢе®һйӘҢе‘ЁжңҹеҚҠдёӘжңҲпјҢйў„еӨ„зҗҶеҸҜд»Ҙз®ҖеҢ–дёәдёүж¬ЎеӣһжөҒгҖӮ

Q5

иҜ·й—®еӨ§е®¶еҒҡе°ҒиЈ…еҸҜйқ жҖ§еүҚзҡ„FTж—¶пјҢжүҖжңүжЁЎеқ—е…ЁйғҪиҰҒиҝҮеҗ—пјҹ

A5

жҳҜзҡ„пјҢеҠҹиғҪе’ҢOSйғҪиҰҒжөӢиҜ•гҖӮ

Q6

еҗ„дҪҚеӨ§дҪ¬пјҢPCTжҲ–иҖ…еҸҢ85е®һйӘҢеӨҡе°‘е°Ҹж—¶еҸҜд»ҘзӯүеҗҢдәҺжҲ–иҖ…еӨ§дәҺMSL3дёӯзҡ„еҗёж№ҝжғ…еҶөпјҹ

A6

PCTеҸҢ85 24hзӣёеҪ“дәҺжҒ’жё©жҒ’ж№ҝз®ұ60в„ғ 60%RH 40hгҖӮ

Q7

иҜ·ж•ҷдёҖдёӢпјҢеҒҡPTC(power temperature cycleпјүж—¶пјҢйңҖиҰҒдҪҝз”ЁжңҖеӨ§е·ҘдҪңз”өеҺӢеҗ—пјҹиҝҳжңүиҙҹиҪҪжңүиҰҒжұӮеҗ—пјҹ

A7

ж ҮеҮҶдёҠжІЎжңүеҶҷиҰҒжұӮжңҖеӨ§зҡ„е·ҘдҪңз”өеҺӢпјҢеҶҷзҡ„еҗҲйҖӮзҡ„Bias пјҢжҜ”иҫғеҫ®еҰҷгҖӮиҙҹиҪҪд№ҹжІЎжңүжҳҺзЎ®зҡ„иҰҒжұӮгҖӮдҪҶжҳҜеҹәжң¬дёҠеә”иҜҘжҳҜдҪ жңҖеёёз”Ёзҡ„е·ҘдҪңжЁЎејҸжқҘ PTCзҡ„жҳҜжҜ”иҫғеҗҲйҖӮпјҢжҲ–иҖ…дҪ йҖүдҪ жңҖдёҘиӢӣзҡ„е·ҘдҪңжЁЎејҸпјҢжҲ‘и§үеҫ—йғҪеҸҜд»ҘгҖӮ

Q8

еҗ‘еҗ„дҪҚеүҚиҫҲиҜ·ж•ҷеҮ дёӘHASTжөӢиҜ•жқҝи®ҫи®Ўзҡ„й—®йўҳпјҡ1гҖҒиҠҜзүҮзҡ„HASTжөӢиҜ•жқҝ и®ҫи®ЎеҺҹзҗҶиҰҒжіЁж„Ҹе“Әдәӣпјҹ2гҖҒиҠҜзүҮзҡ„HASTжөӢиҜ•жқҝйңҖиҰҒJTAGдёӢиҪҪзЁӢеәҸеҗ—пјҹ3гҖҒиҠҜзүҮзҡ„HASTжөӢиҜ•жқҝи®ҫи®Ўж—¶йңҖиҰҒжҠҠиҠҜзүҮеј•и„ҡй—ҙйҡ”дёҠжӢүгҖҒдёӢжӢүе°ұиЎҢеҗ—пјҹ

A8

1. е°ҪйҮҸи®©иҠҜзүҮе·ҘдҪңеңЁдҪҺеҠҹиҖ—пјҢdieзҡ„жё©еҚҮе°ҸпјҢжҜ”еҰӮжҠҠReset pinдёҖзӣҙдҝқжҢҒеӨҚдҪҚзҠ¶жҖҒпјҢCLK pinд№ҹдёҚз»ҷж—¶й’ҹдҝЎеҸ·гҖӮ2. еӣ дёәиҠҜзүҮдёҚйңҖиҰҒе·ҘдҪңпјҢе°ұдёҚиҰҒJTAGдёӢзЁӢеәҸдәҶгҖӮ3. з”өжәҗpinжӯЈеёёжҺҘз”өжәҗпјҢIOй—ҙйҡ”дёҠдёӢжӢүпјҲйҖҡиҝҮ4.7KжҲ–10Kз”өйҳ»пјүд»ҘдҝқжҢҒеҸҜиғҪеӯҳеңЁзҡ„з”өдҪҚе·®пјҲBias)

Q9

HASTз”өжәҗи„ҡдёҠз”өйңҖиҰҒеҠ з”өе®№еҗ—пјҹжӯЈеёёе·ҘдҪңж—¶з”өжәҗи„ҡе’Ңең°зӣҙжҺҘжңүдёӘз”өе®№пјҢHASTйңҖиҰҒиҖғиҷ‘еҗ—пјҹ

A9

дёҚйңҖиҰҒпјҢжӯЈеёёе·ҘдҪңзҡ„йӮЈдёӘз”өе®№жҳҜдёәдәҶжҺ§еҲ¶дёҠз”өж–ңзҺҮе’ҢиҝҮеҶІжҠ–еҠЁзҡ„пјҢз»ҷз”өжәҗж»ӨжіўгҖӮHASTжң¬иә«е°ұз”ЁеӨ–йғЁзӣҙжөҒз”өжәҗйҖҡиҝҮи¶…й•ҝиө°зәҝиҝһиҝҮеҺ»зҡ„пјҢиҝҮеҶІе’Ңж–ңзҺҮйғҪеҸҜжҺ§пјҢжҖ•иҝҮеҶІеҸҜд»ҘеҠ пјҢ然еҗҺз”өе®№д№°зӮ№еҘҪзҡ„гҖӮеҲ«еӣ дёәз”өе®№жҚҹеқҸеҜјиҮҙе®һйӘҢеӨұж•ҲгҖӮ

Q10

иҜ·й—®MCCжңәеҸ°жҳҜеҗҰеҸҜд»Ҙиҫ“еҮәе·®еҲҶдҝЎеҸ·е‘ўпјҹ

A10

еҸҜд»Ҙзҡ„пјҢLC2е’ҢHPB-5CйғҪж”ҜжҢҒзҡ„гҖӮ

Q11

еҗ„дҪҚ专家еҘҪпјҢйҮ‘зәҝдәҢз„ҠзӮ№гҖҒй•Җ银и·ҹй“ңжЎҶжһ¶д№Ӣй—ҙиҝҷз§ҚеҲҶеұӮеҸҜиғҪжҳҜд»Җд№ҲеҺҹеӣ пјҢз»Ҳз«ҜеҸҚйҰҲзҡ„пјҢжңүд»Җд№Ҳж–№жі•еҸҜд»ҘйӘҢиҜҒе‘ўпјҹ

A11

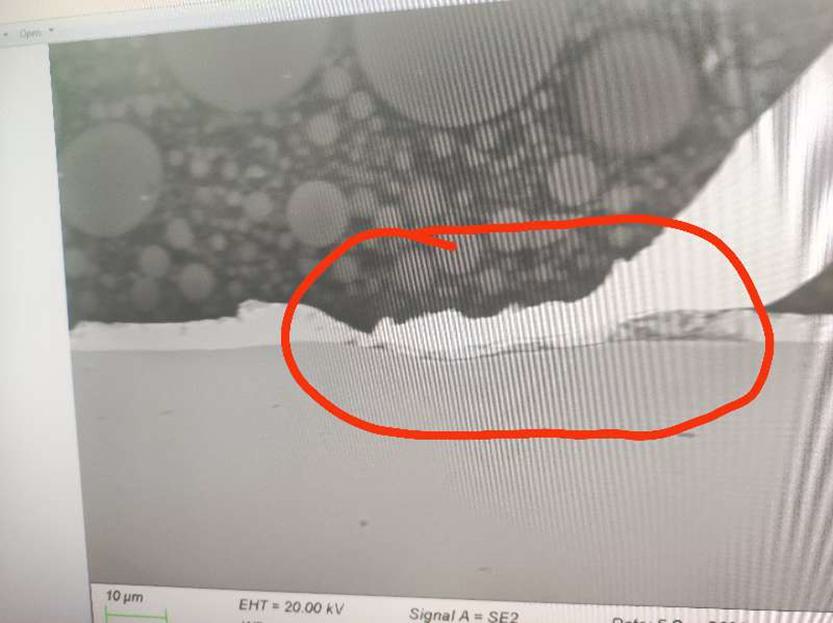

жңүеҸҜиғҪжҳҜе°ҒиЈ…и„ұеұӮ or жү“зәҝиҙЎйҮ‘дёҚиүҜпјҢж–№жі•пјҡ1.ж ·е“Ғе…Ҳжү«sat зңӢжңүжІЎжңүи„ұеұӮ 2.еҒҡжҲҗд»ҪеҲҶжһҗзңӢжңүжІЎжңүжұЎжҹ“ пјҢеҸҰеӨ–йңҖеҗҢж—¶жҜ”еҜ№е…¶д»–жӯЈеёёеҢәеҹҹгҖӮ

Q12

еҗ„дҪҚеӨ§дҪ¬пјҢжңүеҮ зүҮжҷ¶еңҶиЎЁйқўеҮәзҺ°дәҶи№ӯеҲ’дјӨејӮеёёпјҢиҜ·й—®жңүжІЎжңүд»Җд№ҲеҠһжі•еҸҜд»Ҙеҝ«йҖҹжөӢйҮҸеҲ’дјӨж·ұеәҰпјҹWaferиҝҳжңӘеҲ’зүҮпјҢиҠҜзүҮPADй“қеұӮеӨ§иҮҙеңЁ4umе·ҰеҸіпјҢиЎЁйқўеҲ’дјӨдј°и®Ўеә”иҜҘдёҚи¶і1umпјҢдё»иҰҒжҳҜжғійҖҡиҝҮжөӢйҮҸеҲ’дјӨж·ұеәҰиҜ„дј°дёҖдёӢиҙЁйҮҸйЈҺйҷ©гҖӮ

A12

еңЁdiesawд№ӢеҗҺжӢҝдёҖйў—еҒҡFIBпјҢиҝҷз§ҚдёҚиғҪеҸӘзңӢеҲ’дјӨж·ұеәҰеҗ§пјҢзӣёиҝ‘metalй—ҙзҡ„жјҸз”өпјҢз”ҡиҮідёӢеұӮеј№еқ‘пјҢpassivationз ҙжҚҹдҝқжҠӨиғҪеҠӣдёӢйҷҚпјҢиҝҷдёӘеј№еқ‘дёҚеҚ•жҢҮpadеҢәеҹҹпјҢеҲ’дјӨдҪҚзҪ®дёӢж–№йғҪжңүеҸҜиғҪгҖӮ

жқҘжәҗпјҡдёҠжө·еӯЈдё°з”өеӯҗ