Q1

请教各位大佬,我们有几个批次CP测试IGSS是OK的,但封装好后IGSS低良,这个怎么界定是晶圆本身问题还是封装问题呀?

A1

Gate to Source 漏电,先FA看看,Decap后,如果漏电消失,我想基本上就是湿气吧。如果没有消失再做die上的分析。

Q2

请教下大家,从现象上分析可能是数字门失效,有什么办法能够定位到具体位置吗?

A2

scan fail的话,ATE应该可以抓fail index,再到EDA tool定位物理位置,在GDS上找到怀疑的管子以及连接它们的metal,Delayer一层层看。需要DFT的人帮忙看一下,DFT拿到ATE fail log,然后用EDA软件进行diagnosis。

Q3

请教下可以定位到某个transistor还是某个逻辑单元?某个逻辑单元有可能会有多个transistor吗?

A3

先定位哪个cell,然后通过GDS定位哪个transistor,最后切PFA。

Q4

如果没有做DFT,仅仅是从功能上判断出数字门电路失效有什么办法吗?

A4

很难,看功能的复杂度。如果你在GDS上能找到,可以试试,不过几率很低。

Q5

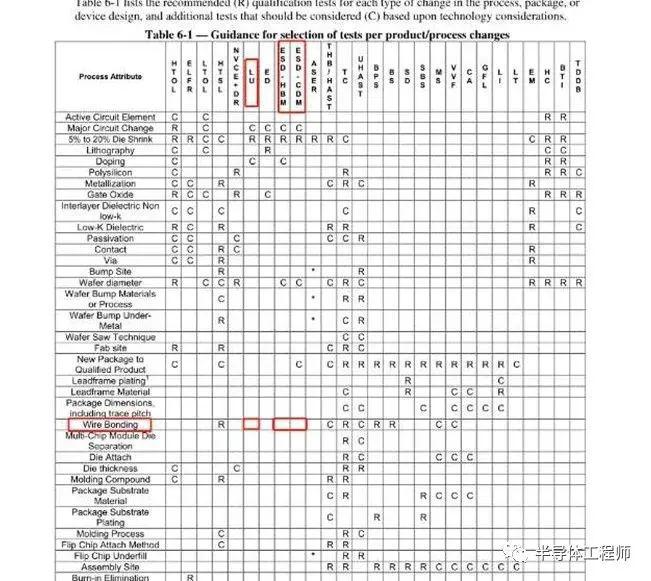

请教一下,更改了bonding不需要复测ESD吗?更改方式为将之前未用到的一个PAD接到引脚上。

A5

建议复测ESD,这个内部pad之前未引出,意味着之前所有的ESD测试都是跳过这个pad。当其与引脚相连时,存在ESD风险。

Q6

各位大佬:请教一个问题,关于晶圆测试前的烘烤,有具体标准和要求么,可以分享下嘛?

A6

烘烤温度80℃ 时间10min。

Q7

各位老板,请教个问题,芯片在"BEWIP Test encounter some issues.",BEWIP Test是指晶圆阶段的测试还是芯片封测阶段的测试呀?

A7

猜测一下,BEWIP Test:BE=backend,WIP=wafer in process, 感觉像是在做inter-metal的WAT测试,不是final的WAT测试。

Q8

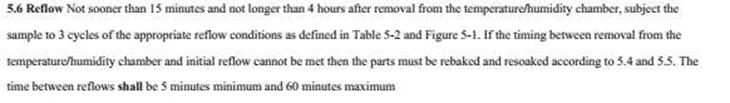

咨询一下,预处理的吸湿和回流焊之间,有没有时间限制啊?

A8

取出15min后4小时内完成3次回流焊。

Q9

请教一下各位大佬, 叠封是否对芯片的HBM有影响, 我们同一wafer的三种不同封装,其中两款单独封装的HBM测试结果为4000V,但是叠封的一款产品HBM测试结果只有3000V。

A9

要看一下ESD是怎么打的,除非叠封很大的延长了PIN脚的连线,才会有影响。另一种可能是打ESD的方式。如果直接在芯片上方打 12kV air discharge, 最上方的芯片是肯定会比较脆弱的。可以评估一下封装上方的Molding厚度,是否起到很好的ESD保护。

Q10

芯片开盖后只开了顶层,如果寄回来之后还能正常上电测试吗?

A10

FIB线路修补不就得开盖再做么,做完还是能拿socket上电测试吧,也可以封完胶再测。

来源:上海季丰电子