大家晚上好,很荣幸能够在CEIA平台上与大家一起探讨半导体封装的学习先进封装技术,希望大家也越来越从这个平台上面能够学到东西。

我今天的分享主要的课题是算力时代先进封装技术的机遇及挑战。

这次主要的报告分为这5个内容。

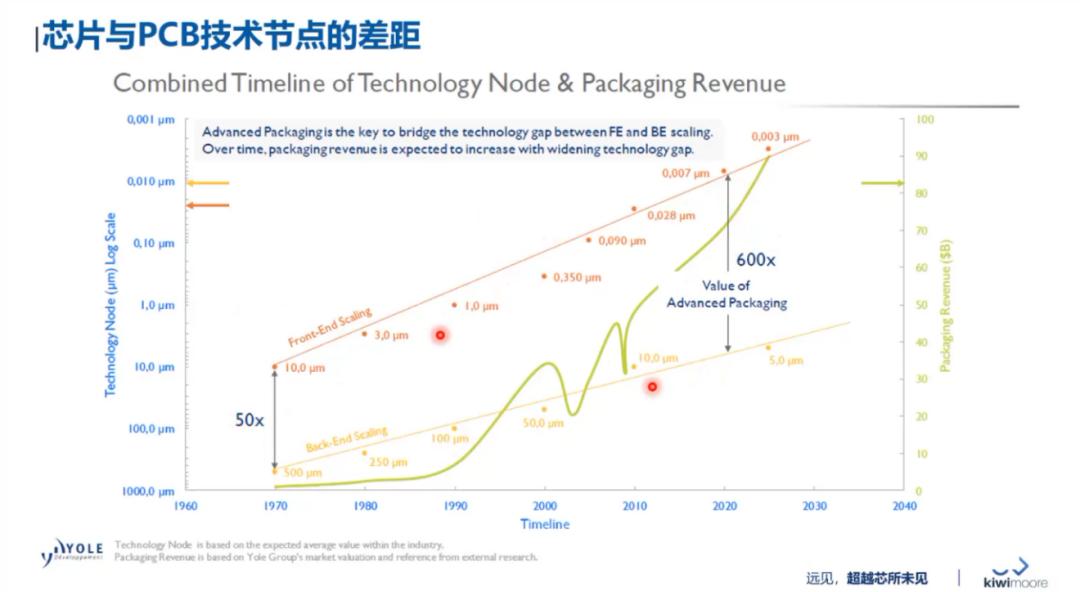

大家可以从上面的报告可以看出,后摩尔时代从60年代到未来2040年,半导体芯片工艺制程能力,从最早的1970年的时候10微米到现在的3纳米,PCB在1970年是500微米,但到现在的PCB的支撑能力就是做的最好的,像日本的厂商,即使是用SIP工艺保持在5微米。

从70年代的时候,可以看到整个芯片跟PCB的差距是在50倍的间距,而到了现在直接已经扩大到600倍差距,代差越来越大,适应代差成为整个发展的行业的趋势。

大家可以看这条曲线,从一开始的封装技术线宽/线距是低于PCB的,那个时候还是用leaded package,包括比如说TO系列的package,但逐渐的会有引入了substrate这个概念,substrate其实就是advanced PCB的理解,substrate level基本上略高于PCB。

但慢慢整个行业,包括大数据的应用,这些AI的应用,PCB其实已经无法满足整个行业的需求,所以引用了先进封装的技术,先进封装的技术就是涉及到硅基的技术,涉及到2.5D的技术,整个行业逐渐的更向硅去靠拢。

这个图就是很好的说明,什么是封装?封装是因为PCB跟硅之间制程能力是有代沟的,有差距的。现在PCB的线宽/线距是100微米级别,而硅现在做的最好的已经3纳米,如何把 PCB的硅信号直接导到PCB正面,所以这是封装要做的事情。

但这封装里面包含了先进封装、传统封装,从传统封装来看包括substrate package,这些package没有就像前道晶圆厂那样去做曝光显影。

而先进封装有很多的技术,其实就是用了曝光显影工艺去做,然后把线宽/线距的再往上拉,最后的密度也往上拉,比如说FAN-IN、FC BGA BUMPING、FANOUT、TSV、BONGING、异面集成,都是先进封装的技术概念,带动整个封装把密度往往上提升,向硅去靠拢,去适应现在所需要的密度。

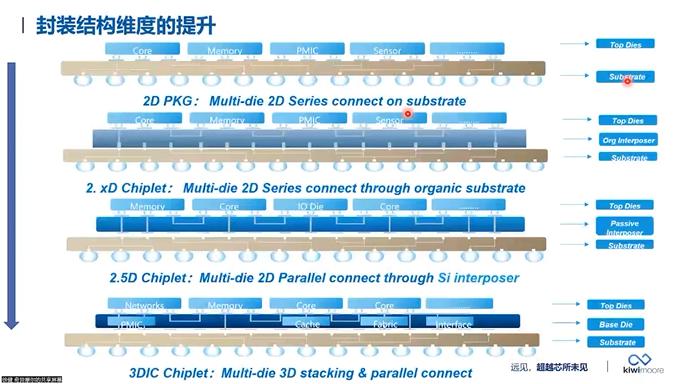

从维度方面,封装的维度方面去看,从最传统2D封装,把所有的芯片都贴在基板上,I/O的数量受限于PCB的substrate的支撑能力,即使是用SiP工艺去做,线宽/线距,10微米以下是非常难达到的。

现在2.5D是在芯片的下端做了一层有机基板,RDL的一层基板,通过这层基板把上面的信号的I/O进行梳理,可以互联的连在一块,不能互联的需要连在PCB板上把信号重新的FANOUT出来,这样最后还是通过substrate把信号引出来,但是更为先进的都还基于在organic substrate的organic interposer的基础上去做这一块。

但是更为先进的,比如说用silicon interposer,可以做到线宽/线距的更近,线宽/线距密度更高,然后上面表面的层数可以做的更高,I/O的数量可以做得更密,但是这样很多出现在先进封装公司,包括FAB去做这一块。

2.5D的理解,就可以看出它在整个芯片跟基板中间加了一颗无源芯片,所以它才会有2.5而不到3这个概念。

最后I/O通过上面interposer进行信号的梳理,然后再通过TSV把信号引到背面的Core4,Core4再连接到基板上面,最后基板上再通过BALL引到外面的整个系统中。

最后再讲一下3D封装,3D其实从名字看出来,可以在三维的Z方向做堆叠的,所以3D封装,是在下面这颗芯片下面,不是passive interposer,而是实实在在的die,die可以支撑上面的其他芯片,上面信号可以独立的去做特别专业的事情,比如CPU专门去做算例,而辅助的功能,包括PMIC、Cache、Interface、I/O可以连接在下面芯片,然后通过下面芯片来跟上面形成crosstalk,把信号之间互联都通过,还有一些信号需要连接到外面,同样在下面芯片里面有TSV,通过与Core4连接,基板再通过连接到外面整个系统,形成system的概念,其实chiplet的本质上在我看来应该也是一种system,类似于更高端的SIP。

总结一下,2D不能算chiplet,而是传统的封装方式,从2.1D到3D这块,其实才是真正的起步chiplet的封装概念。

可以看到像很多像台积电、英特尔,在FANOUT、SOIC,台积电的台积的SOIC的技术,这其实都是在3D技术,它们都是基础的chiplet技术。

整个chiplet与传统封装的技术的优缺点,其实我这边就做了简单的列举,第一个就是I/O的密度,其实传统封装,像倒装封装和Wafer-Bump封装。

应用在chiplet上I/O的数量肯定最高的,FC中等、Wafer-Bump其次,但设备的配置、投入厂房的成本,TSV一定是最低,倒装焊其次。芯片的速度的损耗跟高频性能,TSV是直接上片芯片,对着下面芯片直接上,所以它的距离是最短的,损耗是最低的,而倒装焊的Bump高度其实是很短的,排在中等,最其最差的就是Wafer-Bump,因为Wafer-Bump要拉一根很长的线弧,这些损耗是比较大的。

封装的成本,TSV肯定是最高的,倒装焊会其次,但封装的周期,因为TSV封装涉及到SiP,我不是说简单的芯片流片,还做考虑到TSV的钻孔,TSV的露头,包括先进封装,先进封装了以后其实还是要做传统封装,稍后会讲到。

技术的成熟度,倒装跟Wafer-Bump其实已经非常成熟了,其实的TSV的封装还是在慢慢在国内还是正在开发中,目前市场的占比 Wafer-Bump肯定是最高的,FC逐渐在增多,像TSV相信未来应用、发展趋势会越来越好,特别是现在被美国制裁以后,需要用到先进芯片工艺制程,没有地方去做流片,可能就要弯道超车,是从封装方面去做chiplet的方面去考虑这个问题的,所以chiplet的是另外一条发展,所以它会发展非常的迅速非常的快。

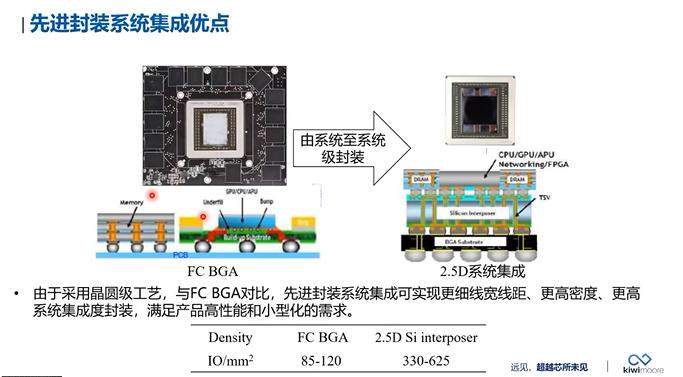

从chiplet可以看,FC BGA就是单颗基板的来料。它的I/O数量是整个基板上封装里面最密的,单位平方毫米的I/O的数量可以做到100左右。

但是如果采用了2.5D Si interposer,可以达到330~625数量级。所以从数量看,其实未来特别是高算力I/O数量特别要求特别多的地方场合,Si interposer的2.5D 包括3D应用是非常的广泛的。

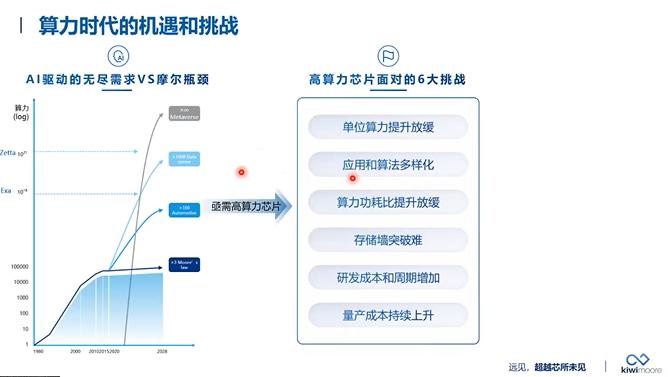

下面我给大家介绍一下整个chiplet的技术方向。从图上可以看出算力时代正在发展,因为后摩尔时代开始,从自动驾驶,数据中心再到最近很火的元宇宙。其实对算力的要求基本上都是成指数增长的要求,像元宇宙直接是无穷大增长,去要求整个电子行业做对外算力的要求。

其实遇到的挑战,第一个就是单位算力的提升和放缓,因为知道现在先进的制程工艺到了3纳米、7纳米以下,其实工艺能力很难再上去,所以单位面积下面去做更多的晶体管,这条路其实很难去实现。

第二点,应用及算法多样化,最近很多汽车,特别是智能汽车智能驾驶,包括元宇宙,大家越来运用越来越广,所以这样算法也越来越多。

第三点,算力功耗比的放缓,算力与功耗比相应的放缓。

第四个,存储墙的壁垒,比如希望存储单元和算力单元离得更近,这样带宽会更高。如果传统的封装很难去做到,因为存储芯片跟CPU芯片可能不在一块,就相应地会传输路径会很长,损耗也非常大。

第五点,研发成本、周期成本非常高,算力要求非常高,所以成本周期会非常长。

第六点.量产的成本持续上升,如果比如说用7纳米转成3纳米,这样整个成本会上升几倍或甚至几十倍状态。

所以我想解决方案是什么?第一个就是同构的扩展,第二个就是同异构的计算,第三点就是异构集成。

首先同构集成从成本方面来看,芯片去流片的时候,芯片的良率跟单颗芯片的unit size是非常有关系的,以前我也算过150平方毫米的芯片,单颗芯片的良率是在80%,但是如果的芯片做到700平方毫米,它的良率只能降到30%,所以整片wafer没有能产出多少颗芯片,所以可以看到很多大公司更愿意把整个芯片去拆分,把整个大面积的芯片拆成几个小面积的,然后同样功能的通过封装组成大的系统。

第二个就是同构性能的提升。现在知道同步性能方面,主要是所有的芯片把很多功能的模块都集中在芯片里面,所以芯片的面积会非常大,但是它本身是因为有些功能是A,有些功能是B,它不能友好的去做特别专长A功能的工具,有很多附带辅助B功能的东西,也是必须放进去的,这样就影响了整体的性能。所以很多公司就把各这种A功能的B功能的芯片功能都拆分开来,形成性能提升。

第三个就是模块化的拆分,有些A功能芯片,用的可能用的是3纳米,要求是7纳米的工艺,但是B功能的模块,其实要求40纳米也能满足功能,没必要把B功能的东西也做成7纳米的工艺去流片,这样导致它的成本会大幅的提升,可以把B功能的芯片单独拆分出来,专门去流片A功能的专门去7纳米工艺制程流片,这样一是模块化,二是降低成本。

最后一点就是异构的组合。看出就是很多的功能,通过不同的架构,就是刚才说的 7纳米、28纳米、40纳米的架构,可以在不同的方式上去做,做完了以后整体一起把通过chiplet模组新建封装的方法,把整个模块形成了系统,最后形成了可逻辑化编辑的东西。

也包括比如说像MEMS,包括光芯片、异质异构这些东西,也可以集中在这个系统里面,这样更好的便于整个系统发挥更好的作用。

总结一下chiplet的主要优点,第一个,chiplet的各个模块其实可以独立设计的,不需要一家公司全部承载,把所有的模块都分开,拆分给各个小公司,总体最后组成大的模块。

第二个,芯片里面不需要集成那么多的功能,可以把所有的芯片拆分开,良率这样也能保证它的良率。

第三个,大大降低了研发成本,不需要那么大的模块,单模块的研发周期、成本都会降低。

第四个,混合工艺集成,有些模块我可以用28纳米的,有些模块用7纳米的,都是可以分开。

第五个,光照尺寸,大家知道光照尺寸是33×26,所以芯片越大接近甚至超过光照的时候,就无法去做。通过上面几个优点,可以把芯片变小,又不受光照尺寸的限制。

第六个,异构异质的集成的性能可以提升,比如说可以集成三、五组半导体,也可以做光芯片的芯片,都甚至可以结合MEMS的芯片在上面。

最后一点就是芯片有堆叠,从立体方向去解决信号传输的问题,所以它的传输路径是非常短,所以它可以加大整个系统的带宽,这样提高整体性能情况。

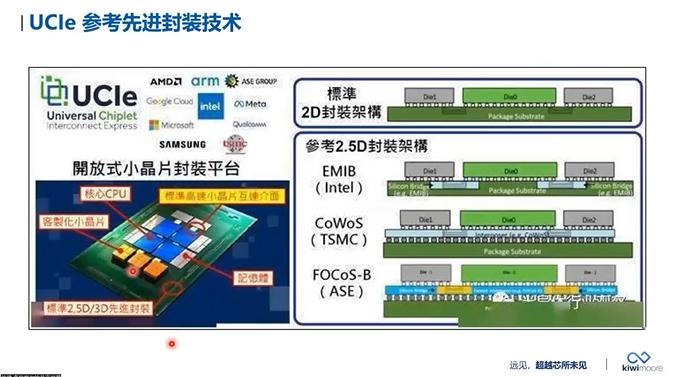

然后针对chiplet的这一块,国际上有UCI的联盟,这个联盟最早有9家公司,这些公司都是国际上的巨头,但专于封测工艺这块有三家,TSMC、英特尔、ASE,UCI联盟讨论工作主要是制定行业的标准,在封装方面,会制定比如micro pump的pitch、size, GTX信号传输MAP的建议。

关于信号会做制定,比如说阻抗、传输路径还有测试的方案,都有去做讨论、规范正在进行中。国内也有标准,无锡有类似的联盟,也在制定相应的方案,我所在的公司也有去参与。

下面给大家介绍封装的chiplet的封装的设计。

从1970年到2020年的整个时间轴去看,从1970年的时候,其实整个封装还只是DIP、QFP这些封装大家可以看比较简单,I/O的数量也不多,那时候其实考虑的问题也不多,function通就行了。

后期逐渐开发出新的封装体系,包括SOP、LCC、PGA这些稍微复杂点,I/O数量稍微多点的封装,用timing持续去看这些问题。

到了90年代,把基板、PCB应用进来了。这个时候可能会考虑更多的就是power功率,特别是频率上升以后,电源下降以后,电源波动对于整个系统是影响非常大,其他包括Reliability,因为用的基板不像lieder Fiene的可靠性那么高,但做substrate毕竟是organic的材料, 所以可靠性要求也比较高。

到2000年,其实更多的是开始有步入先进封装,包括CSP、POP,POP其实也不能算先进封装,因为整个系统越来越集成,热的问题是更值得关注的。

到了10年,其实的先进封装更多的去考虑的包括fanout,包括wafer level CSP。

到了20年,其实目前做的越来越多的做3D方面,就考虑因为是系统,这个结构非常的复杂,而且整个系统的成本是非常贵的,所以更多的考虑chemical、EMI这块,其实跟整个package的研发路径是很匹配的。

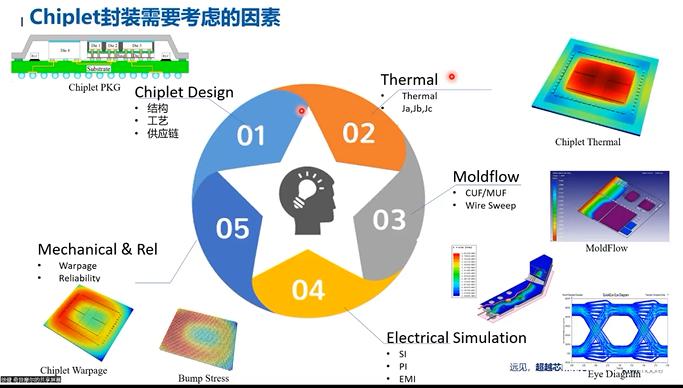

所以总体来看,整个封装设计的时候,需要考虑哪些问题?第一个像在Chiplet设计的时候,肯定会考虑第一位结构。不同于以往,chiplet芯片设计的第一步就是架构。把芯片的封装设计会提到最前面的整个框架结构去考虑问题,同时很重要的是怎么去实现封装和整个工艺。

接下来就是供应链,因为都不成熟,都属于研发阶段,说这供应链怎么去管,用谁家去做Bumping,用谁家做挖孔,用谁家基板,这都是很大的问题。

第二点,热的问题,就是所有的系统就像所有的chiplet的上面有芯片,下面如果是3D,下面那颗芯片如何去散热是个很大的问题。包括的散热到底用什么样的散热盖,用什么样的风冷或水冷的方式,是值得当大课题去做。

然后膜流其实我也把它放在,因为这个膜流其实可以看Top die跟botton die,2.5D或者3D封装的时候,因为往往是用micro pumping去做,大家有可能就micro pump只有40,如果micro pump的size也很小,高度也很低,2.5D的下面interposer跟上面的Top die之间是很小的一条缝,所以如何保证这条缝里面能填充满underfill,后期整个chiplet做molding的时候,怎么样去保证可以在晶圆级的molding去做这个东西,其实是很有挑战的问题,所以膜流这块也会重点去考虑这一块。

电信号这块当然毋庸置疑,包括TDR、PI、PDN、EMI都去考虑这些问题。

最后很关键的就是机械可靠性, package非常的贵,怎么保证它的可靠性,做完以后不会有crack,也是非常大的课题。

特别是在2.5D的时候,最后芯片可能磨成50微米或者100微米的时候,甚至更低的时候,如何保证芯片最后没有crack。而且上面的input上面会组装10或者是10颗、20颗的芯片,这些芯片之间怎么样的应力结合和应力弯曲,这些都是非常大的课题。

所以chiplet是一种封装,是传统封装跟先进封装的结合,又要用到传统封装的技术,也要用到先进封装的技术。

在我看来,封装的设计是整个产品的灵魂,封装如果设计的不好,整个后期在很难去避免去解决问题,所以人家就说质量是设计出来的,一点不为过。

给大家举个例子,比如说汽车里面设计成三个三角轮胎跟设计成圆形轮胎的,无论如何后面再去改善工艺、改善方案,三角轮胎做的肯定是没有圆形轮胎好,所以一定要从设计上去考虑这个问题。

所以这张图大家可以看,这是传统封装Wafer-Bump里面的去考虑的问题,同样适合于chiplet去考虑问题。

从Wafer-Bump来看,整个设计要从头到尾,从工艺的最前头到芯片流片,最后封装测试、可靠性,整体都要去把握做问题。

从弧长/弧高/线材/线径包括分割的分布/距离,每个点其实都是很大的课题去做这一块分析。

来源于CEIA电子智造,作者

赵工

13488683602

zhaojh@kw.beijing.gov.cn

欢迎各公众号,媒体转载,申请加白名单秒通过

投稿/推广/合作/入群/赞助/转发 请加微信13488683602