Intel 22nmе·ҘиүәдёӯпјҢе…ідәҺcontactиҝһзәҝжңүдёӘз»ҶиҠӮе·ҘиүәеҸ«SACпјҢе…Ёз§°еҸ«self-aligned contactпјҢдёӯж–Үзҝ»иҜ‘еҸ«иҮӘеҜ№еҮҶжҺҘи§ҰпјҢжңүиҜ»иҖ…еҗҺеҸ°з•ҷиЁҖжғідәҶи§Је…·дҪ“з»ҶиҠӮпјҢиҝҷзҜҮж–Үз« иҜҰз»Ҷд»Ӣз»ҚдёӢSACе·ҘиүәгҖӮ

з®ҖеҚ•жқҘиҜҙиҜҙпјҢSACе·Ҙиүәе°ұжҳҜеңЁж …жһҒgateдёҠж–№ж·»еҠ дёҖеұӮдҝқжҠӨжҖ§д»Ӣз”өеұӮпјҢзӣ®зҡ„жҳҜйҳІжӯўжәҗпјҢжјҸжһҒзҡ„contactдёҺж …жһҒgateзҹӯи·ҜгҖӮдё»иҰҒеҺҹеӣ жҳҜеҪ“ж—¶contactзҡ„pitchи¶ҠжқҘи¶Ҡе°ҸпјҢsource/drain contactеҫҲе®№жҳ“еҸ‘з”ҹеҒҸ移пјҢйҖ жҲҗдёҺgateзҹӯи·ҜпјҢжңҖз»ҲеҜјиҮҙlow yieldгҖӮ

IntelеңЁе…¶22nm FinFETе·ҘиүәдёӯйҰ–е…ҲжҺЁеҮәSAC flowпјҢдё»иҰҒжҳҜж·»еҠ дәҶдёүдёӘжӯҘйӘӨпјҢе…·дҪ“жөҒзЁӢеҰӮдёӢпјҡ

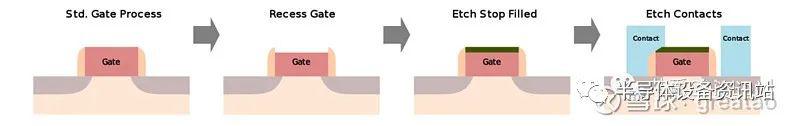

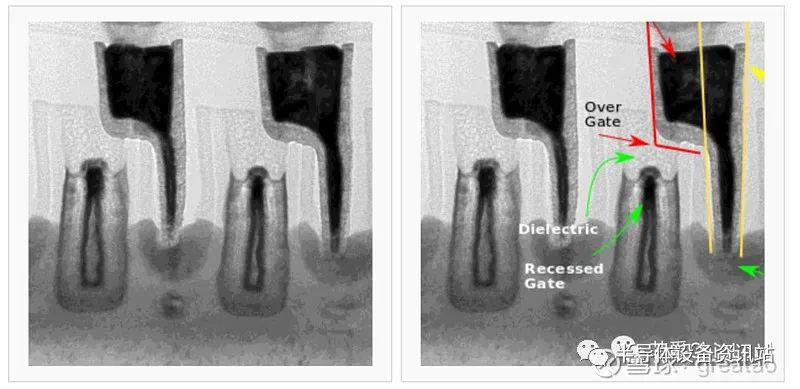

Intelж ҮеҮҶе·ҘиүәеҪўжҲҗmetal gate

metal gateеҗ‘дёӢеҮ№йҷ·

еҗ‘дёӢеҮ№йҷ·зҡ„еҢәеҹҹдёӯеЎ«е……ж°®еҢ–зЎ…etch stop layer然еҗҺCMPзЈЁе№і

然еҗҺиҰҶзӣ–дёҖеұӮж°§еҢ–зЎ…

жңҖеҗҺиҝӣиЎҢcontact patterning

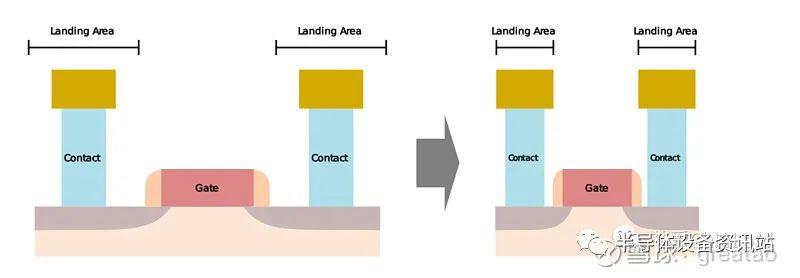

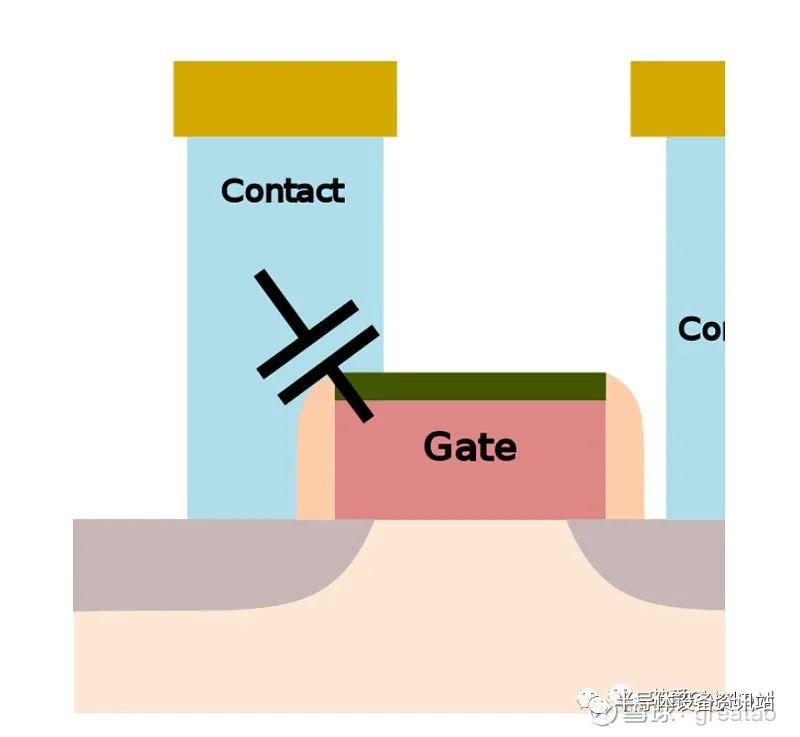

жңҖдё»иҰҒе·®ејӮе°ұжҳҜеңЁmetal gateзҡ„дёҠйқўж·»еҠ дёҖеұӮж°®еҢ–зЎ…е’Ңж°§еҢ–зЎ…пјҢиҝҷж ·еҚідҪҝsource/drainзҡ„contact overlaid on metal gateдёҠпјҢз”ұдәҺж°®еҢ–зЎ…д»Ӣз”өиҙЁеӯҳеңЁпјҢд№ҹдёҚиҮідәҺзҹӯи·ҜпјҢиҝҷж ·е°ұеӨ§еӨ§жҸҗй«ҳдәҶmisalignment marginгҖӮ

дёҠйқўзҡ„дәҢз»ҙеӣҫеҸҜиғҪдёҚеҘҪзҗҶи§ЈпјҢиҝҷйҮҢиҰҒиҜҙжҳҺзҡ„жҳҜпјҢGateдёҠд№ҹжңүcontactпјҢдҪҶжҳҜе’Ңsource/drainзҡ„contactдёҚеңЁеҗҢдёҖж°ҙе№ійқўдҪҚзҪ®пјҢжүҖд»Ҙsource/drainзҡ„contactеҸ‘з”ҹеҒҸ移пјҢеҚідҪҝе’ҢgateжҺҘи§ҰдәҶпјҢеҸӘиҰҒжІЎжңүе’ҢgateдёӢйқўзҡ„йҮ‘еұһжҺҘи§ҰйғҪжІЎжңүе…ізі»пјҢдёҚеҪұе“ҚжӯЈеёёиҝһзәҝгҖӮ

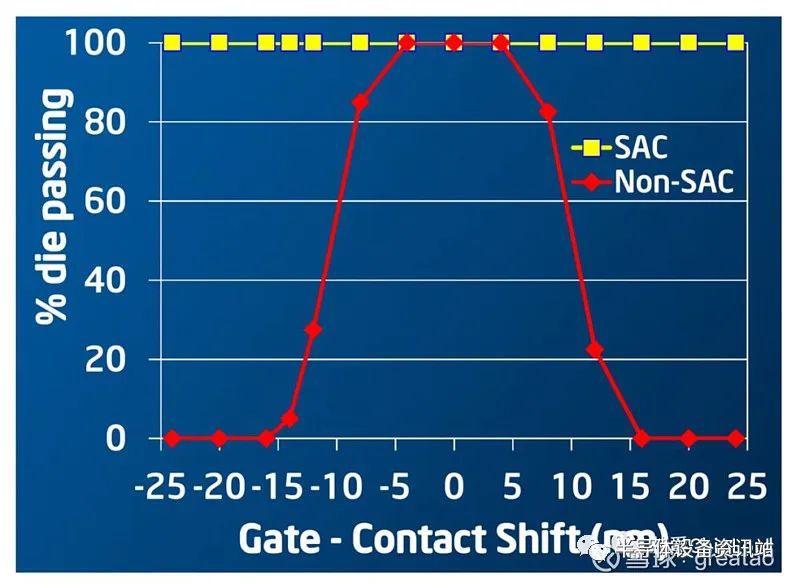

еҰӮжһңжІЎжңүSAC flowпјҢIntle 22nmеҲ¶зЁӢдёӯcontact misalignment marginеҸӘжңү+-5nmпјҢ10nmе·ҰеҸізҡ„misalignmentе°ұдјҡйҖ жҲҗ20%е·ҰеҸізҡ„yield lossпјҢдҪҶжҳҜеўһеҠ дәҶSAC flowд»ҘеҗҺпјҢgate еҲ° contactзҡ„shift marginеҸҜд»ҘиҫҫеҲ°25nmпјҢиүҜзҺҮжҳҫи‘—жҸҗй«ҳгҖӮ

зҺ°еңЁзңӢжқҘпјҢSAC flowеҫҲз®ҖеҚ•пјҢеҸӘдёҚиҝҮдәҶеўһеҠ еҮ жӯҘprocessпјҢдҪҶжҳҜиҝҷеңЁеҪ“е№ҙеҫҲжңүеҲӣйҖ жҖ§пјҢиҖҢдё”ж•ҲжһңйқһеёёжҳҺжҳҫпјҢеӨ§еӨ§жҸҗй«ҳдәҶиүҜзҺҮпјҢдёҚеҫ—дёҚиҜҙintelзҡ„е·ҘзЁӢеёҲиҝҳжҳҜйқһеёёеҺүе®ізҡ„

жқҘжәҗпјҡеҚҠеҜјдҪ“и®ҫеӨҮиө„и®Ҝз«ҷпјӣдҪңиҖ…пјҡgreatao

иөөе·Ҙ

13488683602

zhaojh@kw.beijing.gov.cn

ж¬ўиҝҺеҗ„е…¬дј—еҸ·пјҢеӘ’дҪ“иҪ¬иҪҪпјҢз”іиҜ·еҠ зҷҪеҗҚеҚ•з§’йҖҡиҝҮ

жҠ•зЁҝ/жҺЁе№ҝ/еҗҲдҪң/е…ҘзҫӨ/иөһеҠ©/иҪ¬еҸ‘ иҜ·еҠ еҫ®дҝЎ13488683602